# ELECTROMECHANICAL LIFTING ACTUATION OF A MEMS CANTILEVER AND NANO-SCALE ANALYSIS OF DIFFUSION IN SEMICONDUCTOR DEVICE DIELECTRICS

by

#### IMEN REZADAD

B.S. Shahid Beheshti University, 2008

M.S. Iran University of Science and Technology, 2010

M.S. University of Central Florida, 2013

A dissertation submitted in partial fulfillments of the requirements

for the degree of Doctor of Philosophy

in the Department of Physics

in the College of Sciences

at the University of Central Florida

Orlando, Florida

Summer Term 2015

Major Professor: Robert E. Peale

© 2015 Imen Rezadad

#### **ABSTRACT**

This dissertation presents experimental and theoretical studies of physical phenomena in micro- and nano-electronic devices. Firstly, a novel and unproven means of electromechanical actuation in a micro-electro-mechanical system (MEMS) cantilever was investigated. In nearly all MEMS devices, electric forces cause suspended components to move toward the substrate. I demonstrated a design with the unusual and potentially very useful property of having a suspended MEMS cantilever lift away from the substrate. The effect was observed by optical micro-videography, by electrical sensing, and it was quantified by optical interferometry. The results agree with predictions of analytic and numerical calculations. One potential application is infrared sensing in which absorbed radiation changes the temperature of the cantilever, changing the duty cycle of an electrically-driven, repetitively closing micro-relay.

Secondly, ultra-thin high-k gate dielectric layers in two 22 nm technology node semiconductor devices were studied. The purpose of the investigation was to characterize the morphology and composition of these layers as a means to verify whether the transmission electron microscope (TEM) with energy dispersive spectroscopy (EDS) could sufficiently resolve the atomic diffusion at such small length scales. Results of analytic and Monte-Carlo numerical calculations were compared to empirical data to validate the ongoing viability of TEM EDS as a tool for nanoscale characterization of semiconductor devices in an era where transistor dimensions will soon be less than 10 nm.

To my wife and best friend, Javaneh, who is on my side all the time.

#### **ACKNOWLEDGMENTS**

This research was funded by Florida high tech corridor I-4 program and NanoSpective, Inc. for which I thank both of these institution. I also acknowledge department of Physics at university of central Florida for providing assistantship opportunities.

I would like to thank Prof. Robert Peale, my advisor for his great guidance and encouragements during my research in this PhD program. Also thanks to Dr. Brenda Prenitzer, CEO and President of NanoSpective, Inc. who has been a great mentor in both research and work for me in past two years.

I would also like to thank my colleagues and friends at NanoSpective, Inc. and our research group, Ms. Maureen Burns, Dr. Stephen Schwarz, Dr. Brian Kempshall and Dr. Henry Williams, Evan Smith, Pedro Figueiredo, Farnood Rezaie, Janardan Nath, Deep Panjwani, Doug Maukonen and Guy Zummo for all of their helps in this research.

A lot of thanks to my parents, Mr. Alireza Rezadad and Mrs. Aghdas Razzazifar who always encouraged me in the path of learning and education. I also acknowledge supports of my beloved grandparents and aunt who are always in my thoughts with their kind memories.

At the end, I would like to give special thanks to my beloved wife, best friend and great colleague, Javaneh Boroumand. She had a major role especially in the first project presented in this dissertation which I am grateful for. I owe her a great deal of my success. Thanks god for her and all other blessings in my life.

# **TABLE OF CONTENTS**

| LIST OF FIGURES xii                                     |

|---------------------------------------------------------|

| LIST OF TABLESxxi                                       |

| CHAPTER 1 INTRODUCTION1                                 |

| 1.1 History of Semiconductors                           |

| 1.2 Microelectromechanical Systems and Infrared Sensing |

| 1.3 Understanding of Semiconductor and MEMS Devices     |

| 1.4 Outline of This Dissertation                        |

| CHAPTER 2 PATENT REVIEW AND DEVICE DESIGN9              |

| 2.1 Introduction                                        |

| 2.2 Review of Preliminary Work                          |

| 2.3 Design Criteria                                     |

| 2.3.1 Thermal Bending                                   |

| 2.3.2 Thermal Time Constant                             |

| 2.3.3 Thermomechanical Noise                            |

| 2.4 Device Design                                       |

| CHAPTER 3 SEMI-ANALYTICAL APPROACH24                    |

| 3.1 Introduction                                        |

| 3.2 Electrostatic Field in a System of Conductors       |

| 3.3  | Energy in Electrostatic Field of Conductors | . 25 |

|------|---------------------------------------------|------|

| 3.4  | System of Two Flat Conductors               | . 27 |

| 3.5  | Three Parallel Plate Problem: Real Case     | . 28 |

| 3.6  | Repulsive Electrostatic Force               | . 29 |

| 3.7  | Conclusion                                  | . 33 |

| CHAP | TER 4 FINITE ELEMENT MODELING               | . 34 |

| 4.1  | Introduction                                | . 34 |

| 4.2  | Fundamentals of Finite Element Modeling     | . 34 |

| 4.3  | FEM Software Packages                       | . 38 |

| 4.   | 3.1 Gmesh: Grid Generator                   | . 38 |

| 4.   | 3.2 Elmer: FEM Solver                       | . 40 |

| 4.4  | Device Modeling and Results                 | . 43 |

| 4.5  | Conclusion                                  | . 48 |

| СНАР | TER 5 FABRICATION                           | . 50 |

| 5.1  | Introduction                                | . 50 |

| 5.2  | Buried Plate Fabrication                    | . 51 |

| 5.3  | Surface Plate and Tip Pad                   | . 52 |

| 5.4  | Anchors and Tip Fabrication                 | . 53 |

| 5 5  | Arms and Cantilever                         | 55   |

| 5.6  | Release                                                   | . 58 |

|------|-----------------------------------------------------------|------|

| 5.   | .6.1 Hardened ProLift                                     | . 59 |

| 5.   | .6.2 Solution to Hardened ProLift                         | . 62 |

| 5.7  | Device Dimensions                                         | . 65 |

| 5.8  | Contact Pads and Final Device                             | . 68 |

| 5.9  | Conclusion                                                | . 73 |

| CHAP | TER 6 DEVICE CHARACTERIZATION                             | . 74 |

| 6.1  | Introduction                                              | . 74 |

| 6.2  | Curvature and Stress Measurement                          | . 74 |

| 6.   | 2.1 Theoretical Considerations                            | . 80 |

| 6.   | .2.2 Results and Discussion                               | . 83 |

| 6.3  | Device Experimental Test Setup                            | . 85 |

| 6.4  | Device Characterization Results                           | . 87 |

| 6.5  | Conclusion                                                | . 92 |

| CHAP | TER 7 TRANSISTORS AND THEIR CHARACTERIZATION              | . 94 |

| 7.1  | Introduction                                              | . 94 |

| 7.2  | Field Effect Transistors                                  | . 95 |

| 7.   | 2.1 Structure and Function of FET                         | . 95 |

| 7    | 2.2 Advancements in MOSFET technology: High-k Dielectrics | 97   |

| 7.3 Physical and Chemical Characterization of Nano-Transistors |

|----------------------------------------------------------------|

| 7.3.1 Transmission Electron Microscopy (TEM)                   |

| 7.3.2 Energy Dispersive X-ray Spectroscopy                     |

| 7.3.3 Energy Electron Loss Spectroscopy                        |

| CHAPTER 8 THEORY OF TEM and EDS RESOLUTION 115                 |

| 8.1 Introduction                                               |

| 8.2 Potential Sources of TEM Artifacts                         |

| 8.3 Electron Source Types                                      |

| 8.4 Electron Beam Characteristics                              |

| 8.4.1 Beam Brightness                                          |

| 8.4.2 Energy Coherence and Spatial Coherence                   |

| 8.4.3 Beam Diameter                                            |

| 8.5 TEM and EDS Spatial Resolution                             |

| CHAPTER 9 TEM PARAMETERS OPTIMIZATION                          |

| 9.1 Introduction 128                                           |

| 9.2 Monte Carlo Simulation of Electron interaction             |

| 9.3 Monte Carlo Simulation Tools                               |

| 9.3.1 Casino v3.2                                              |

| 9.3.2 MC X-Ray Lite v1.2                                       |

| 9.4 TEM Parameter Study and Their Optimization                | 133 |

|---------------------------------------------------------------|-----|

| 9.4.1 Beam Diameter                                           | 134 |

| 9.4.2 Beam Spacing                                            | 137 |

| 9.5 Sample Thickness Effect                                   | 140 |

| 9.6 Conclusion                                                | 143 |

| CHAPTER 10 DIFFUSION DETECTION BY EDS LINE SCAN               | 144 |

| 10.1 Introduction                                             | 144 |

| 10.2 Diffusion Effect in Simulations                          | 144 |

| 10.3 Sample Preparation                                       | 148 |

| 10.3.1 Teardown                                               | 149 |

| 10.3.2 Decapsulation                                          | 150 |

| 10.3.3 Light Optical and IR Microscopy                        | 151 |

| 10.3.4 Cross Section and Plan View Polishing                  | 152 |

| 10.3.5 Focused Ion Beam (FIB)                                 | 157 |

| 10.4 TEM Images and EDS Line Scans                            | 161 |

| 10.5 EDS Line Scans Simulation and Comparison with Experiment | 170 |

| CHAPTER 11 CONCLUSION                                         | 172 |

| APPENDIX: PUBLICATIONS                                        | 178 |

| LIST OF REFERENCES                                            | 181 |

# LIST OF FIGURES

| Figure 2-1 Simplified schematic of the device. [18]                                                      |

|----------------------------------------------------------------------------------------------------------|

| Figure 2-2 Timing diagram showing applied bias $V_{\text{B}}$ and measured tip voltage $V_{\text{T}}$    |

| waveforms. [19]                                                                                          |

| Figure 2-3 Focal plane array configuration of final devices.                                             |

| Figure 2-4 Demonstration of double layer system bending due to differences in therma                     |

| expansion coefficient of layers.                                                                         |

| Figure 2-5 (Left) Top view of deflection map due to the stress caused by uniformly applied               |

| pressure of 154 N/m2 applied to the rigid 20 x 18 $\mu m^2$ cantilever plate. (Right) Side view          |

| of the cantilever displacement scaled up by a factor of 10. [19]                                         |

| Figure 2-6 Tip height ramp vs time with superimposed vibrational noise. [19]                             |

| Figure 2-7 Overall structure of the device.                                                              |

| Figure 3-1 Schematics of simplified three plate system for this device                                   |

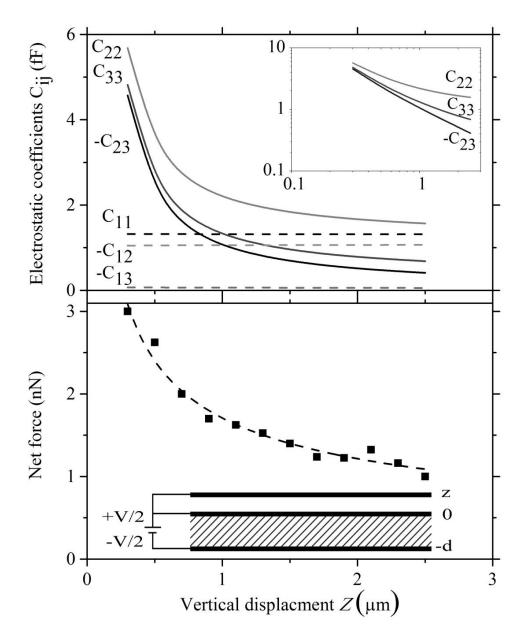

| Figure 3-2 (upper) Coefficients $C_{ij}$ for system of three parallel square plates as a function        |

| of the cantilever height z for plate area 10 $\mu m$ x 10 $\mu m$ . Inset: log-log plot for three of the |

| curves. (lower) Net force on 10 $\mu m$ x 10 $\mu m$ cantilever vs. its height above the surface fo      |

| 20 V bias. Symbols are calculation results. The line is a fit to 1z. Inset: Model schematic              |

| [18]                                                                                                     |

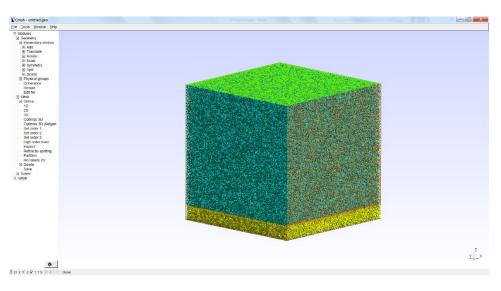

| Figure 4-1 Screen shot of Gmesh with a designed and meshed 3D cube with different layers                 |

| and physical properties on each surface.                                                                 |

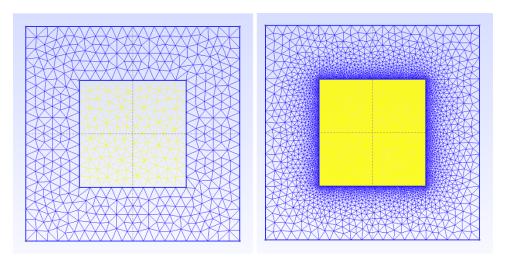

| Figure 4-2 Comparison of single value mesh size (left) and location dependent mesh size                  |

| (right)                                                                                                  |

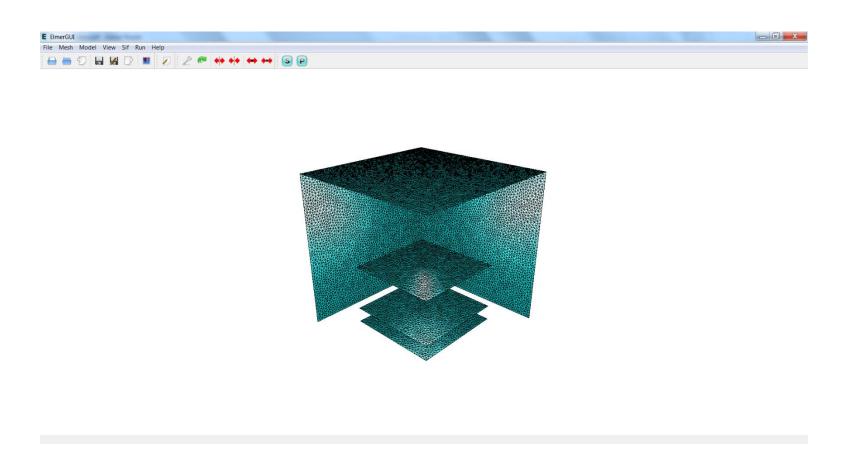

| Figure 4-3 ElmerGUI Interface. Shown object is meshed 3D model of three plate capacitor.               |

|--------------------------------------------------------------------------------------------------------|

| Some of surrounding world walls are hidden to show 3 plates. Volume mesh is also hidden.               |

|                                                                                                        |

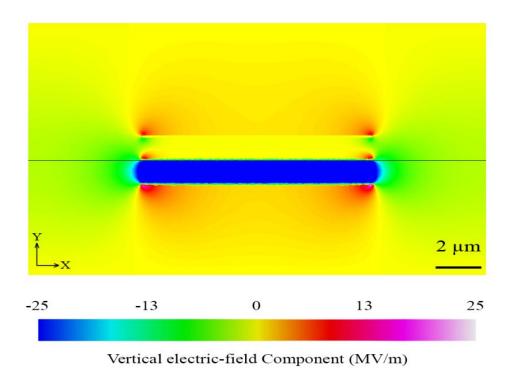

| Figure 4-4. Electric field distribution of $10~\mu m$ long 3 parallel plate system. Top and middle     |

| plates are at $+20~V$ while bottom plate is held at $-20~V$ . Gaps between plates are 1 $\mu m$ . [24] |

| 44                                                                                                     |

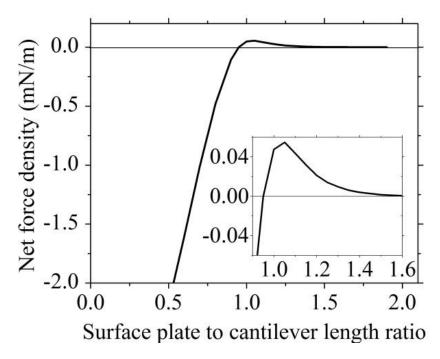

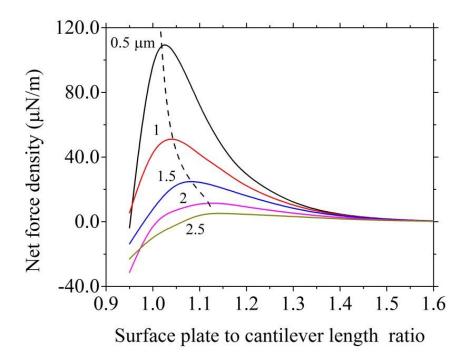

| Figure 4-5 Net force density vs. size of the surface plate relative to that of the cantilever.         |

| [24]45                                                                                                 |

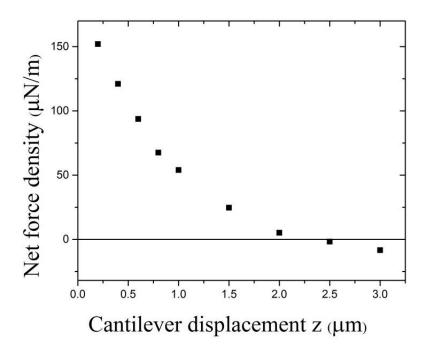

| Figure 4-6 Net force density vs. cantilever displacement. [24]                                         |

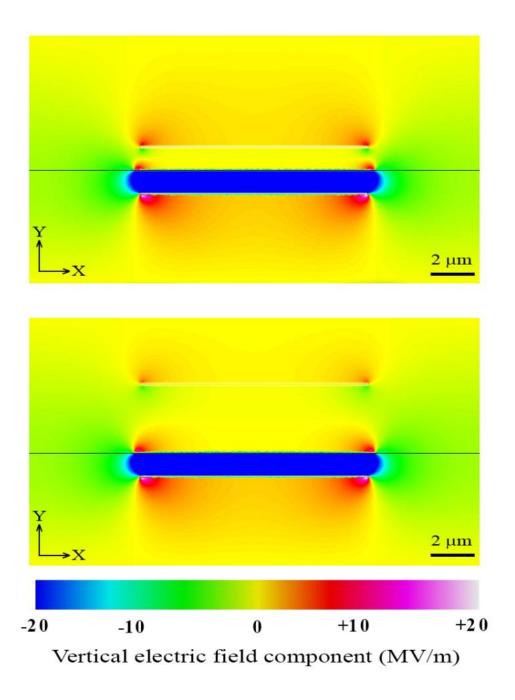

| Figure 4-7 Distribution for the vertical component of the electric field vector (V/m) for z            |

| = 1 (top) with repulsive force on top plate and 3 $\mu m$ (bottom) with attractive force on top        |

| plate. Dark line in the middle shows where surface is located.[24]                                     |

| Figure 4-8 Force Density vs. surface plate to cantilever length ratio for cantilever heights           |

| z. The z values are indicated next to each curve in microns. [18]                                      |

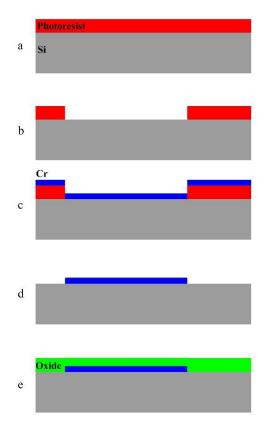

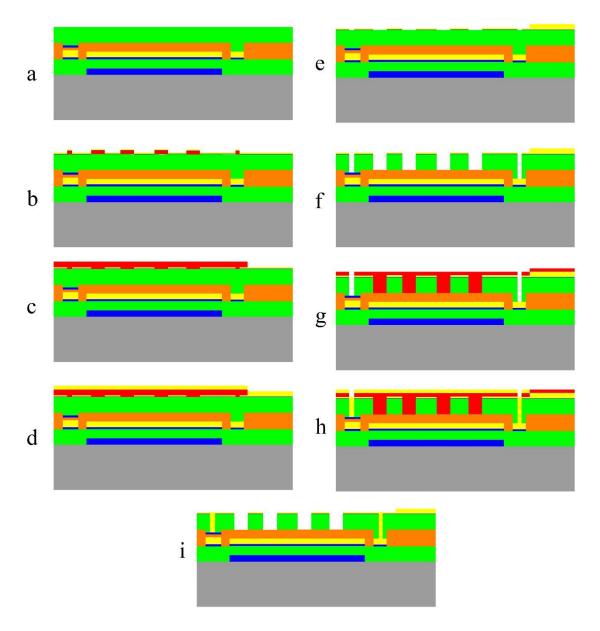

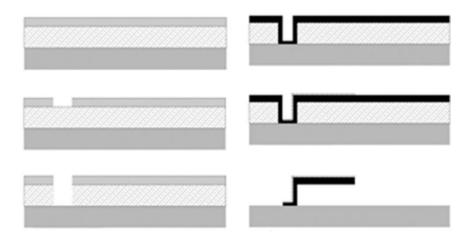

| Figure 5-1 Steps in fabrication of buried plate. a) Spin coating Si with photoresist and               |

| baking. b) Photolithography and pattering resist with buried plate mask. c) 100 nm Cr                  |

| deposition. d) Lift off. e) 500 nm silicon dioxide PECVD deposition                                    |

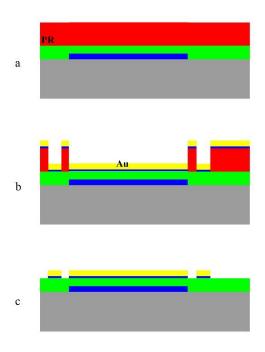

| Figure 5-2 Processing steps for fabrication of surface plate. a) Photoresist spin coating. b)          |

| 10 nm Cr and 100 nm Au deposition. c) Lift off                                                         |

| Figure 5-3 Summarized fabrication process for tip, anchors and structure oxide. a) Starting            |

| with pre-patterned surface plate, tip pad and anchor pad. b) Sacrificial layer (ProLift) spin          |

| coating. c) Photoresist spin coating and creating anchors pattern into ProLift d) Spin                 |

| coating, patterning and Cr deposition for Tip metal. e) Lift off. f) PECVD SiO <sub>2</sub> deposition. |

|---------------------------------------------------------------------------------------------------------|

|                                                                                                         |

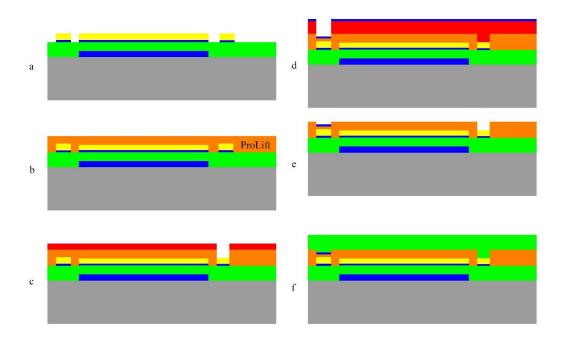

| Figure 5-4 Fabrication process for top metal plate and providing electrical connection                  |

| between plate, tip and metals under anchors. a) Starting point. b) Photoresist spin coating,            |

| patterning and metal deposition for release holes and access via to tip and anchor pad. c)              |

| Photoresist spin coating and patterning for additional metal on bimorph arms. d) Au                     |

| deposition. e) Lift off. f) RIE with CF4 using metal masks to create access via to tip and              |

| anchors pad and release holes. g) Photoresist spin coating and patterning for anchors and               |

| tip access via. h) Angled Au deposition. i) Lift off                                                    |

| Figure 5-5 (Solid triangles) Wet development depth vs. time for bare 1.5 $\mu m$ thick                  |

| Prolift100-20 in MF319 developer at room temperature with PMMA mask and 100 micron                      |

| pattern size. (Open triangles) Wet development for hard-baked ProLift (30 min at 300 C)                 |

| with other conditions the same. (Solid squares) Dry plasma etch depth vs. time for 1.2 $\mu m$          |

| ProLift and 1 mm pattern size (Open squares) Dry etch data for hard-baked ProLift with                  |

| other conditions the same. 60                                                                           |

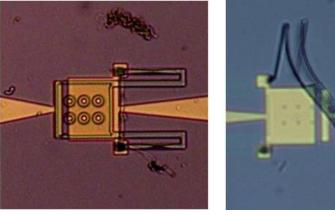

| Figure 5-6 (Left) Optical microscope images of cantilevers during wet release process in                |

| MF319. ProLift sheets are coming off the structure. (Right) A cantilever broken by floating             |

| intact sheets of ProLift                                                                                |

| Figure 5-7 (Left) Black residue left by dry etching hard baked ProLift in oxygen plasma.                |

| (Right) A cantilever that has been partially released from hard-baked ProLift sacrificial               |

| layer by 55 minutes of oxygen plasma etch. The cantilever arms appear badly eroded by                   |

| ion bombardment                                                                                         |

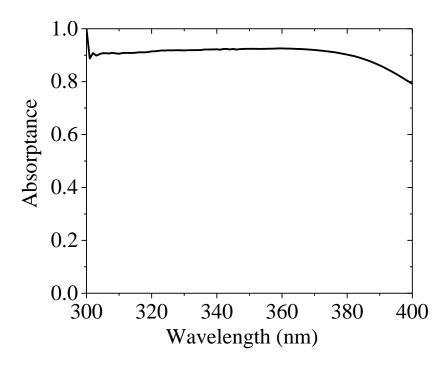

| Figure 5-8 Absorption spectrum of ProLift in the range of 300-400 nm wavelengths 63           |

|-----------------------------------------------------------------------------------------------|

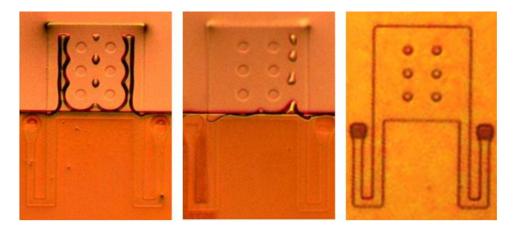

| Figure 5-9 (Left) A partially released paddle after 12 minutes in MF319 developer, while      |

| arms and anchors are covered by PR. (Middle) Paddle is almost released after 22 minutes       |

| in MF319 with PR still present. (Right) PR is striped and the whole cantilever is soaked in   |

| fresh MF319 developer, fully releasing the cantilever after 13 minutes                        |

| Figure 5-10 (Left to right) Optical microscope images of the stages of cantilever release     |

| after 60, 90, and 120 minutes O <sub>2</sub>                                                  |

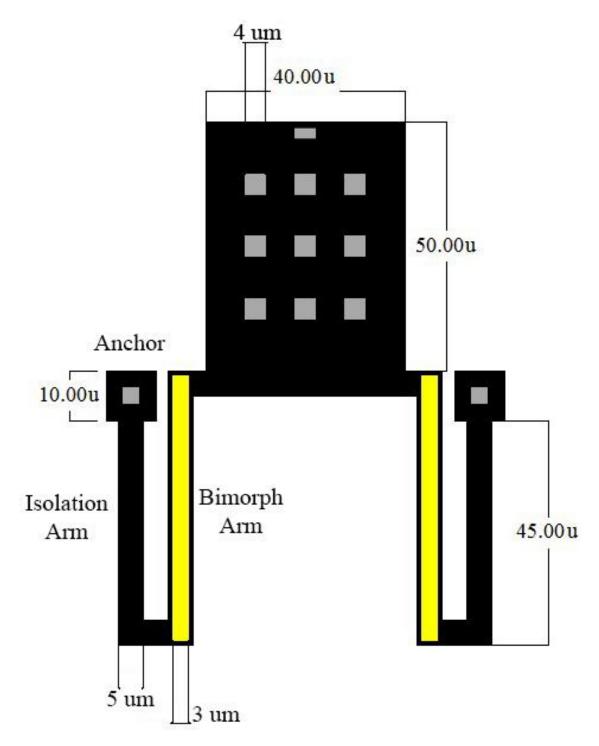

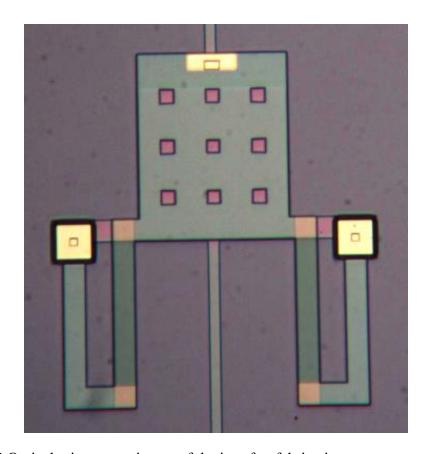

| Figure 5-11 Top view design of single pixel in medium size                                    |

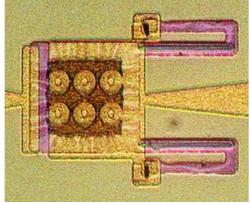

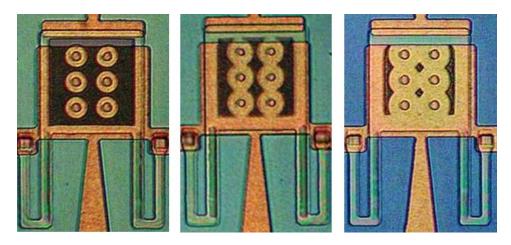

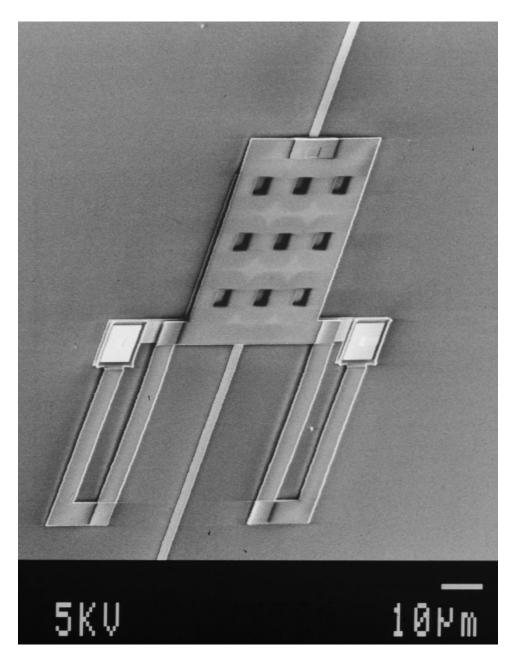

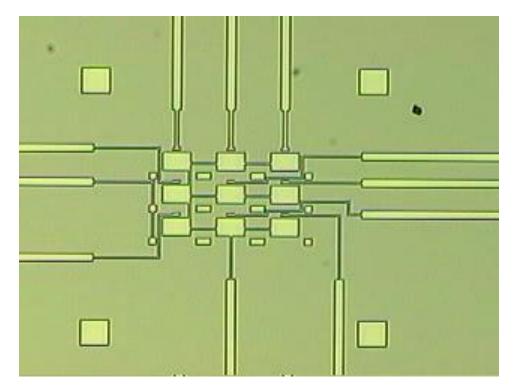

| Figure 5-12 Optical microscope image of device after fabrication                              |

| Figure 5-13 SEM image of a fabricated device                                                  |

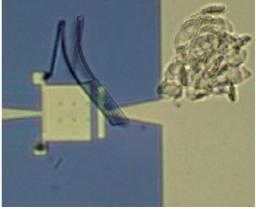

| Figure 5-14 Close up and overall view buried plates and it's corresponding bond pad (top      |

| figures) and surface plates, tip contact pads, anchor pads and their corresponding electrods. |

| (bottom figures) these two patterns are made at two different lavels and are seperated by a   |

| dielectric layer. and RIE etching creates access to buried plate bond pad the the end 70      |

| Figure 5-15 Optical microscope close up of $3 \times 3$ array pad and biasing line regions 71 |

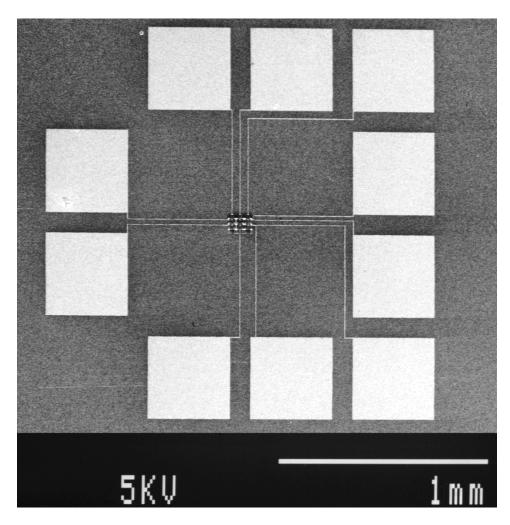

| Figure 5-16 Low magnification SEM image of $3 \times 3$ fabricated array. Optional separate   |

| biasing of anchors (and concesuently top plate) and surface plates are removed in the final   |

| fabricated device without and change to its function                                          |

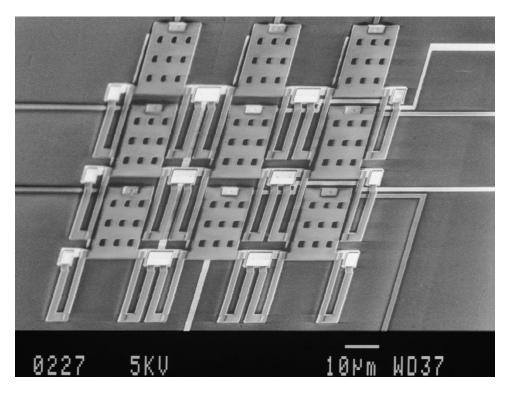

| Figure 5-17 High magnification SEM image of $3 \times 3$ array of final pixels                |

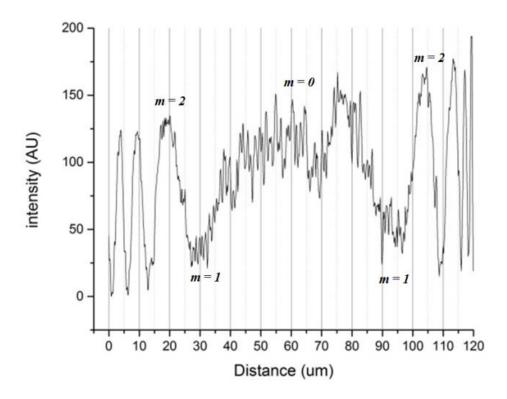

| Figure 6-1 Optical microscope image in monochromatic light, showing Fizeau fringes. 75        |

| Figure 6-2 Fabrication steps of cantilevers: a. Spin ProLift 100-2 as sacrificial layer, then |

| PMMA; b. Pattern PMMA using e-beam writer and development in MIBK:IPA solution;               |

| c. Transfer pattern to sacrificial layer using combination of wet and dry etch; d. PECVD                   |

|------------------------------------------------------------------------------------------------------------|

| SiO <sub>2</sub> ; e. Patterned Au lift-off to achieve oxide etch mask; f. Etch oxide in RIE, then release |

| in O <sub>2</sub> plasma RIE                                                                               |

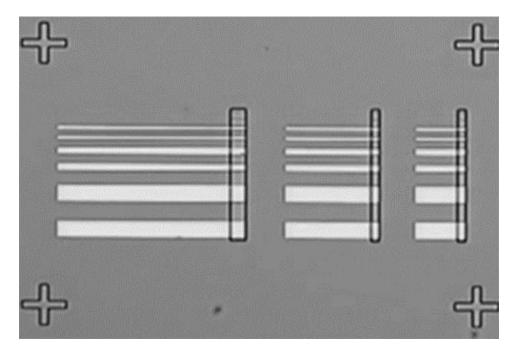

| Figure 6-3 Optical microscope image of cantilever arms with length 55, 120, and 250                        |

| micron and with width 1, 5, 10, and 25 micron. The narrowest arms are invisible in this                    |

| image. All arms are anchored at one end. The image was collected before etching the oxide                  |

| and release from the sacrificial layer                                                                     |

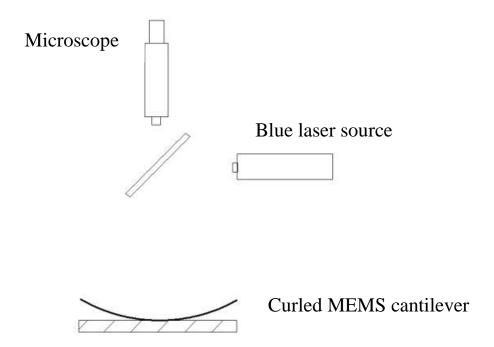

| Figure 6-4 Schematic of set-up for observing Fizeau fringes                                                |

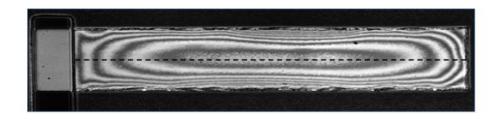

| Figure 6-5 Microscope image of cantilever with results of indicated intensity line-scan. 80                |

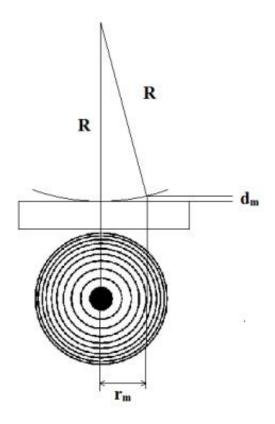

| Figure 6-6 Schematic with air gap $d_m$ , ring radius $r_m$ , and radius of curvature $R$                  |

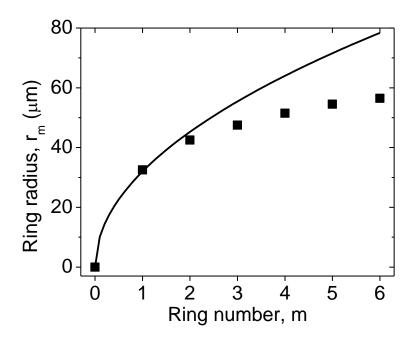

| Figure 6-7 ring radius rm vs. ring number m for figure 66-5 profile (symbols) and function                 |

| 32√m (line)                                                                                                |

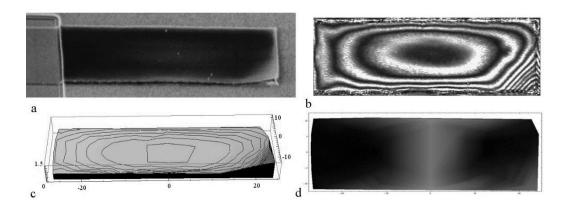

| Figure 6-8 a. SEM image of an arm after release b. Image taken with 408 nm wavelength                      |

| source revealing fringe pattern. c. Contour plot. d. Calculated stress map on the surface of               |

| cantilever, bright areas shows higher stress values. 84                                                    |

| Figure 6-9 Front view of created LabVIEW interface used for testing devices                                |

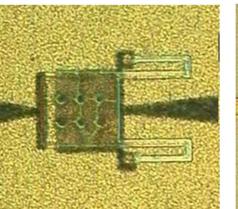

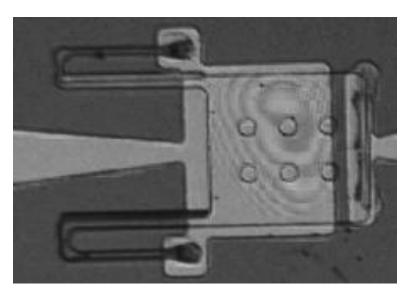

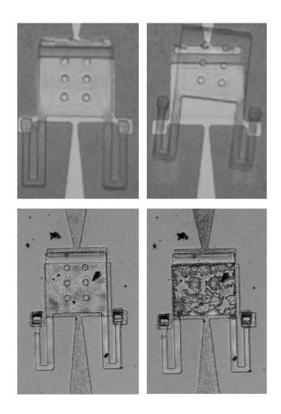

| Figure 6-10 Video microscopy frames of well-released cantilever before (upper left) and                    |

| after (upper right) reaching 40 V applied bias, where upward electrostatic force has ripped                |

| the cantilever off its anchors. Video frames for incompletely released cantilever before                   |

| (lower left) and after (lower right) applying bias. Electrostatic force lifts the cantilever               |

| from polyimide residue, causing air bubbles to intrude under the semi-transparent                          |

| cantilever from the edges and release holes.                                                               |

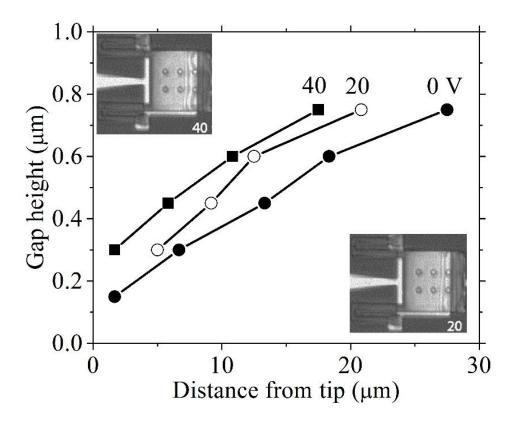

| Figure 6-11 Height of gap between surface plate and cantilever as function of distance from   |

|-----------------------------------------------------------------------------------------------|

| tip for three values of applied bias. Insets show images with different interference patterns |

| in red light at 20 V and 40 V.                                                                |

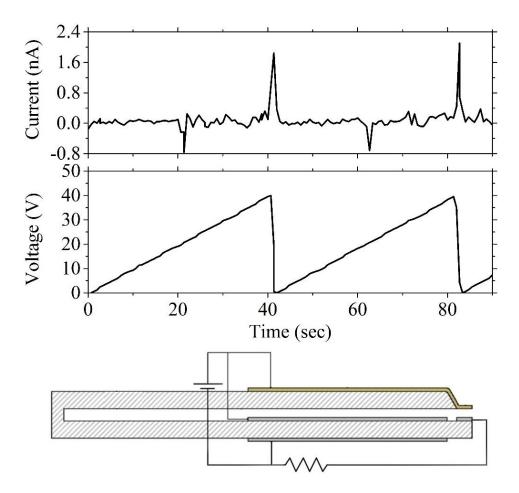

| Figure 6-12 (top) Applied sawtooth ramp bias applied between cantilever and buried plate      |

| and measured current through load resistor. (bottom) Schematic of device with external        |

| circuitry91                                                                                   |

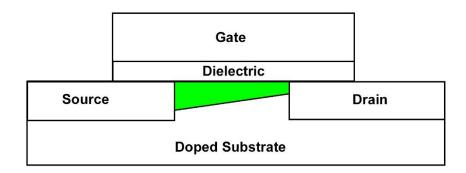

| Figure 7-1 Simple MOSFET Structure, highlighted region is the current channel 96              |

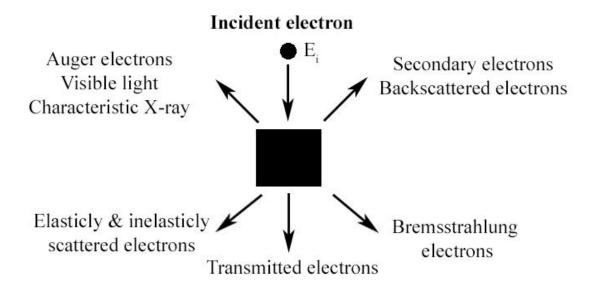

| Figure 7-2 Some important signals generated by the interaction of high-energy electrons       |

| with a specimen. 103                                                                          |

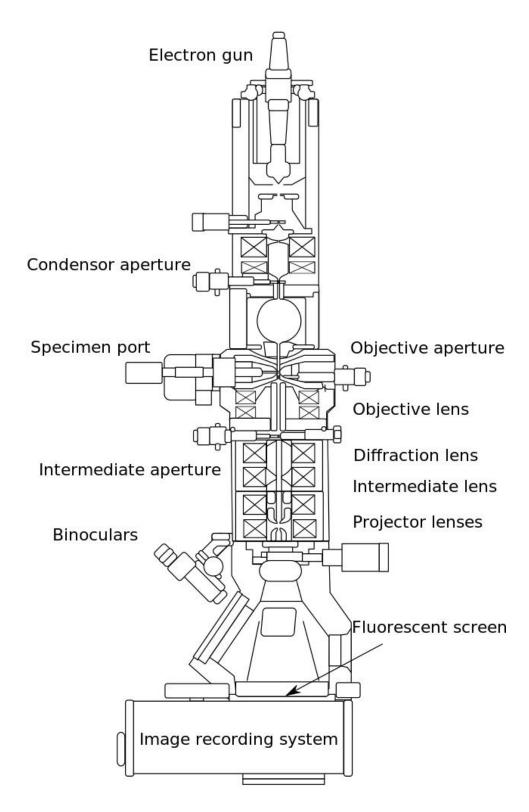

| Figure 7-3 Schematic diagram of a Transmission electron microscope. [71] 108                  |

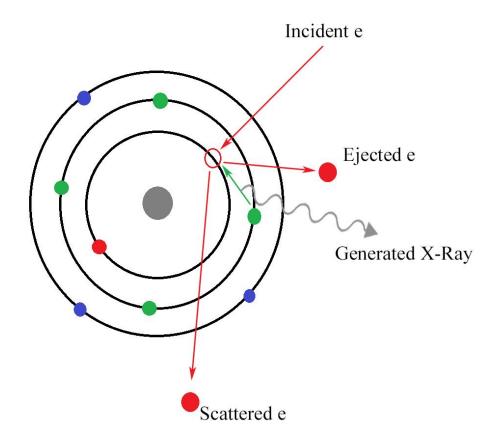

| Figure 7-4 Characteristic X-ray generation caused by the interaction of a high energy         |

| electron with a core shell electron of an atom                                                |

| Figure 7-5 Schematic diagram of a Si(Li) X-ray detector                                       |

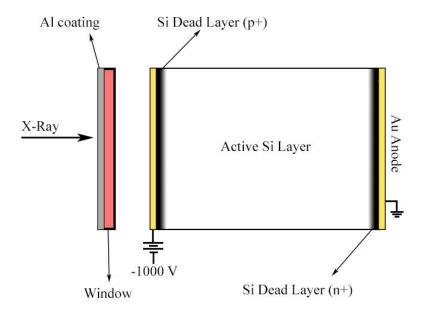

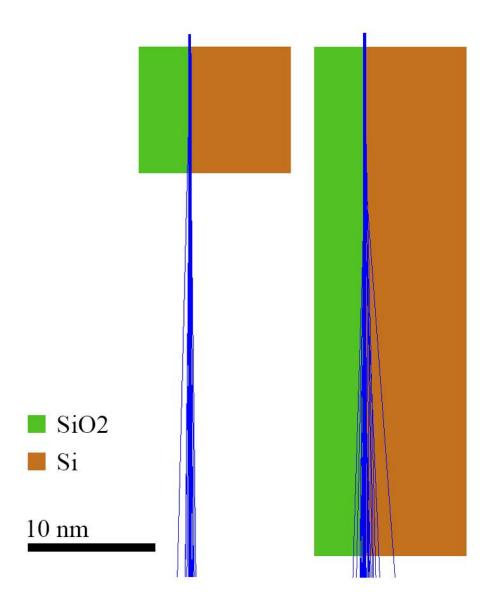

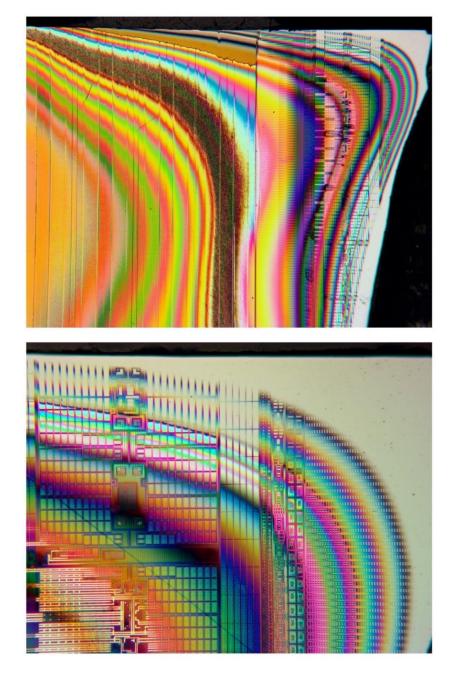

| Figure 8-1 Monte Carlo simulation of TEM electron-sample interaction in 50 nm thick foil      |

| of Si with 100 KeV incident electron beam energy (top) and 300 KeV (bottom). As incident      |

| beam energy increases interaction volume decreases                                            |

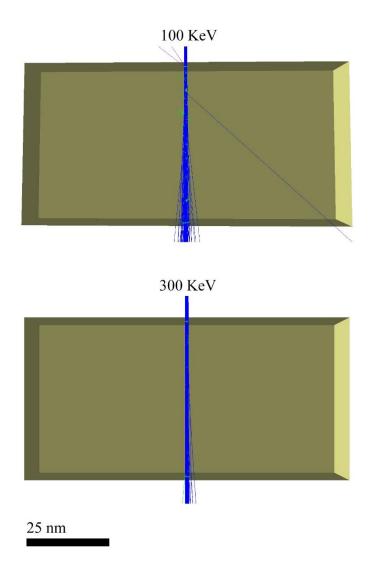

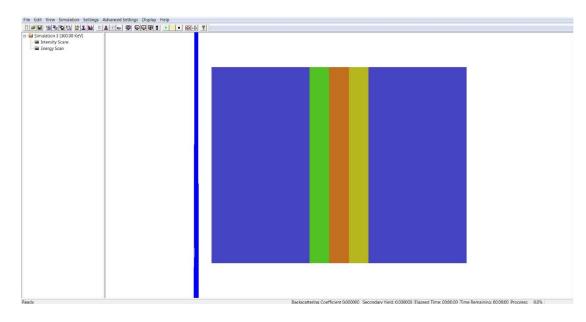

| Figure 8-2 Monte Carlo simulation of SEM electron-sample interaction in 50 µm thick foil      |

| of Si (only portion of sample is shown) with 10 KeV incident electron beam energy (top)       |

| and 30 KeV (bottom). As incident beam energy increases interaction volume increases.          |

|                                                                                               |

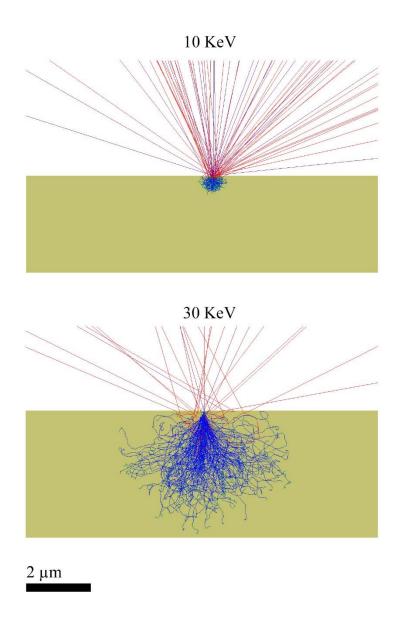

| Figure 9-1 Main interface of Casino v3.2.                                                     |

| Figure 9-2 MC X-Ray Lite Version 1.2 main interface                                           |

| Figure 9-3 Schematic of simulated specimen                                               |

|------------------------------------------------------------------------------------------|

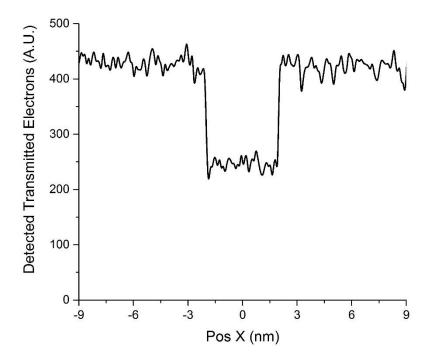

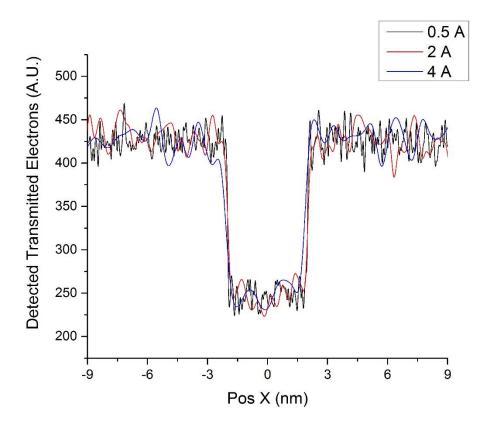

| Figure 9-4 Simulated transmitted electrons counts through Si/SiO2/Si specimen shown in   |

| figure 9-3. A sharp interface is observed.                                               |

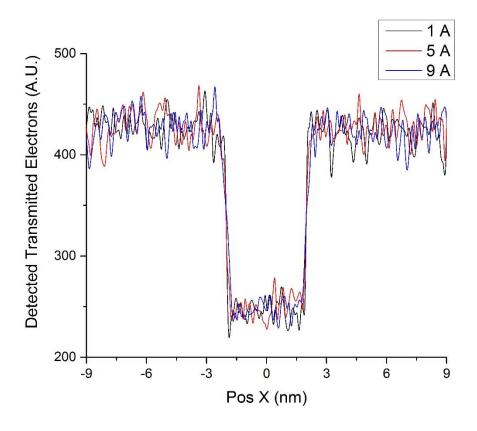

| Figure 9-5 Comparison of transmitted electron signals for 1 A, 5 A and 9 a beam diameter |

| with same beam step size of 1 A                                                          |

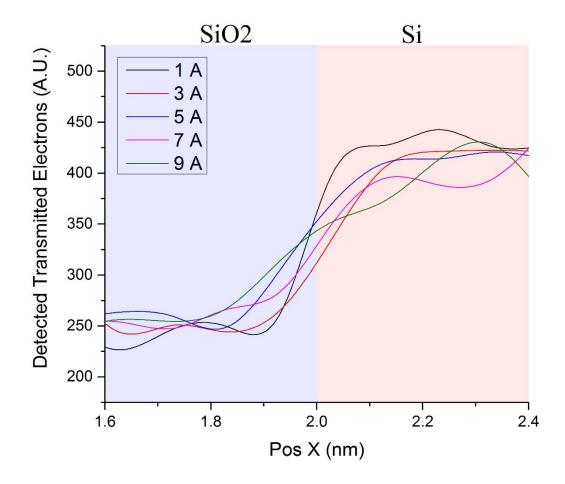

| Figure 9-6 Transmitted electron counts for five different beam diameters with same bear  |

| spacing at the interface region of Si and SiO2                                           |

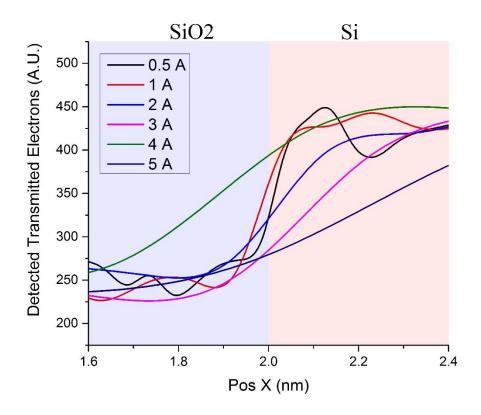

| Figure 9-7 Transmitted electron signal for three different beam spacing                  |

| Figure 9-8 Transmitted electron counts for six different beam spacing with same bear     |

| diameter of 1 Å at the interface region of Si and SiO2.                                  |

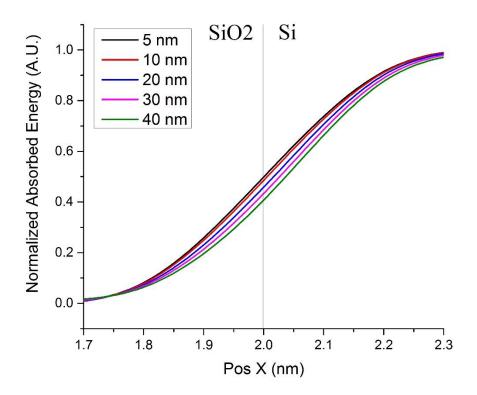

| Figure 9-9 Normalized absorbed energy line scan across SiO <sub>2</sub> /Si interface    |

| Figure 9-10 Comparison of electron beam scattering through 10 nm and 40 nm thic          |

| samples of SiO <sub>2</sub> / Si                                                         |

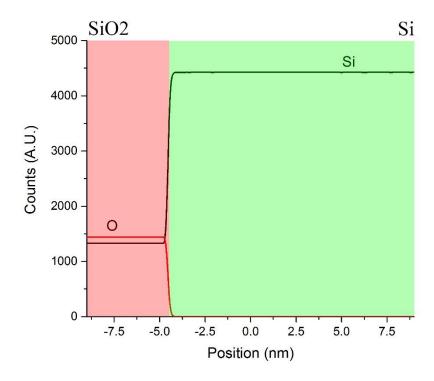

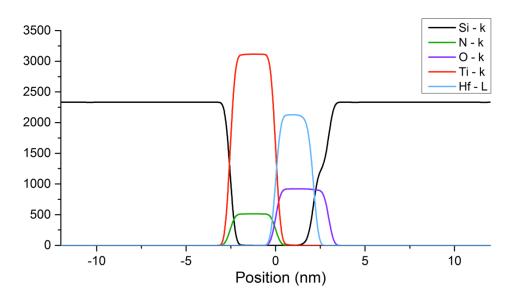

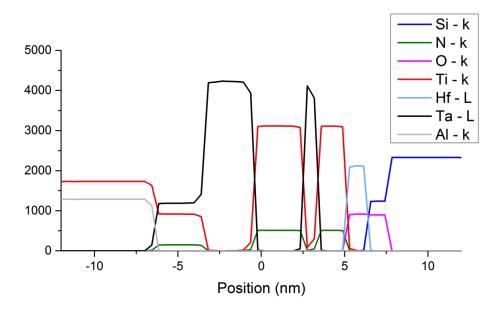

| Figure 10-1 EDS line scan simulation across non-diffused SiO2 / Si interface             |

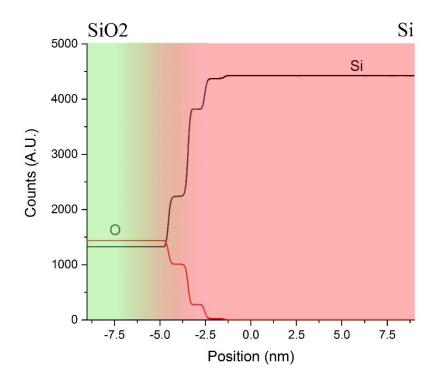

| Figure 10-2 EDS line scan simulation across diffused SiO2 / Si interface with normal     |

| distribution of standard deviation equal to 1                                            |

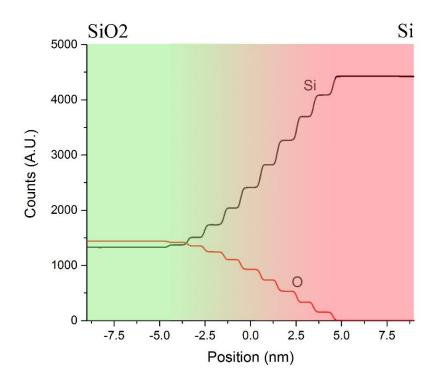

| Figure 10-3 EDS line scan simulation across diffused SiO2 / Si interface with normal     |

| distribution of standard deviation equal to 5                                            |

| Figure 10-4 Example of torn down electronic device to access contained PCBs. Image use   |

| courtesy of NanoSpective, Inc. 14                                                        |

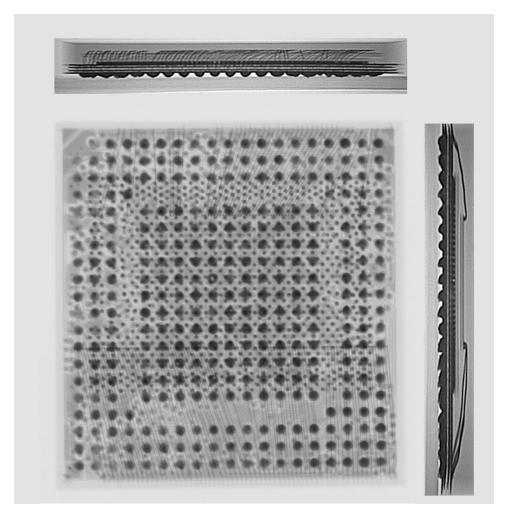

| Figure 10-5 X-ray image of a multi-chip package from different angles. Image use         |

| courtesy of NanoSpective, Inc                                                            |

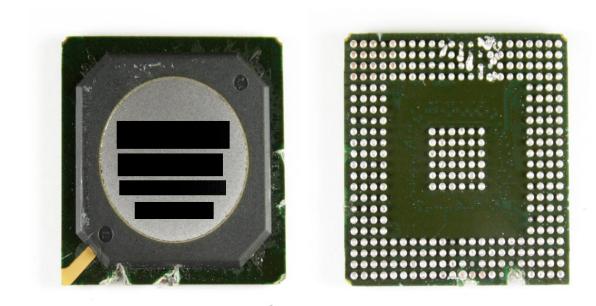

| Figure 10-6 IC package front and back side before removal of packaging materials. Image    |

|--------------------------------------------------------------------------------------------|

| used courtesy of NanoSpective, Inc. 151                                                    |

| Figure 10-7 Front side light optical and back side infrared image of a die. Image used     |

| courtesy of NanoSpective, Inc. 152                                                         |

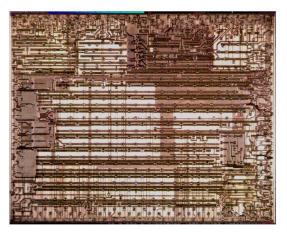

| Figure 10-8 LOM images plan-view bevel polished die showing multiple levels of             |

| interconnect down to substrate. Images shown at two different magnifications reveal        |

| different levels of detail. Image used courtesy of NanoSpective, Inc                       |

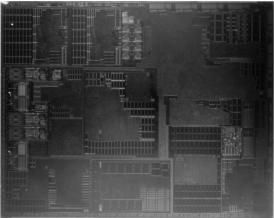

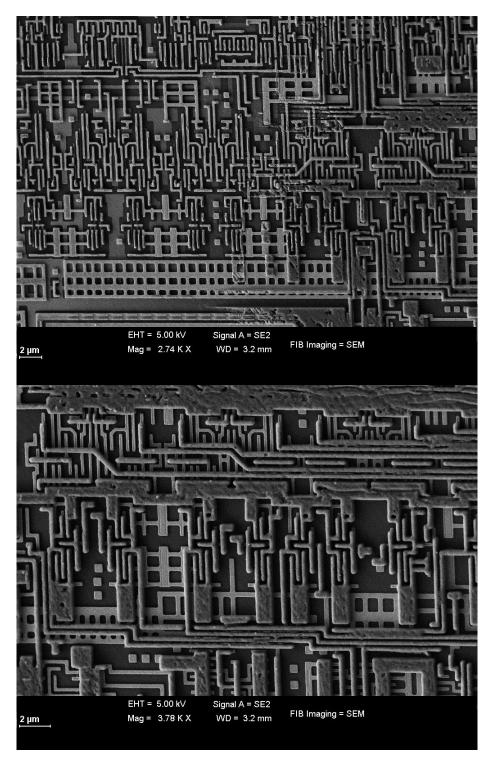

| Figure 10-9 SEM images of sample that was skeleton etched after subsequent to a plan-      |

| view beveled polish. Image used courtesy of NanoSpective, Inc                              |

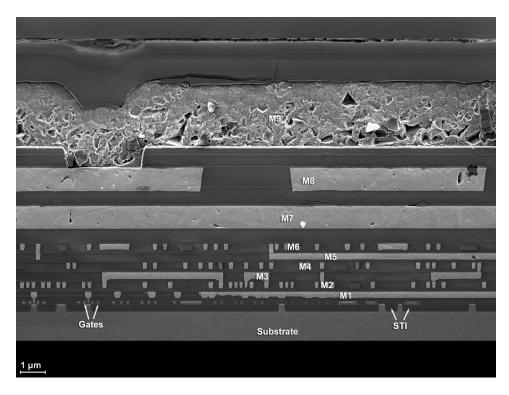

| Figure 10-10 A die cross-section SEM image at low magnification showing all levels of      |

| metallization. Image used courtesy of NanoSpective, Inc                                    |

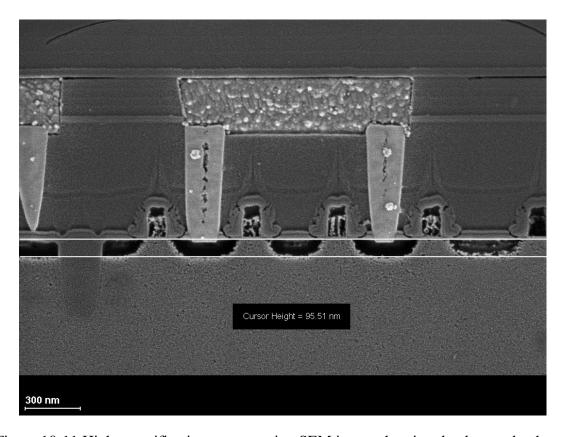

| Figure 10-11 High magnification cross-section SEM image showing the dopant depth and       |

| transistor structure after wet chemical etching. Image used courtesy of NanoSpective, Inc. |

|                                                                                            |

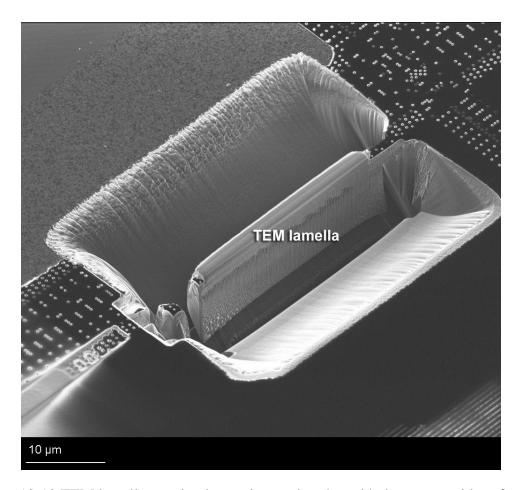

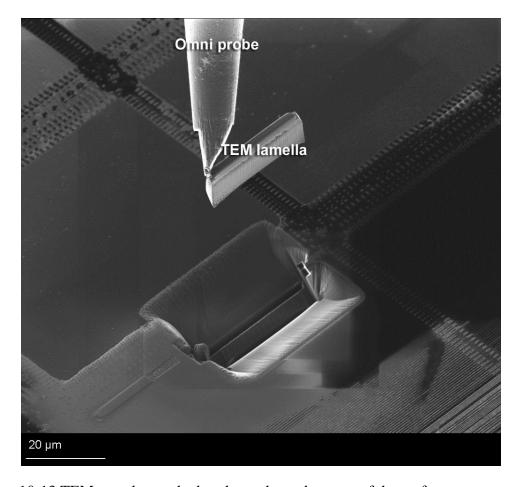

| Figure 10-12 TEM lamella creating by cutting wedge shaped holes on two sides of region     |

| of interest                                                                                |

| Figure 10-13 TEM sample attached to the probe and cut out of the surface                   |

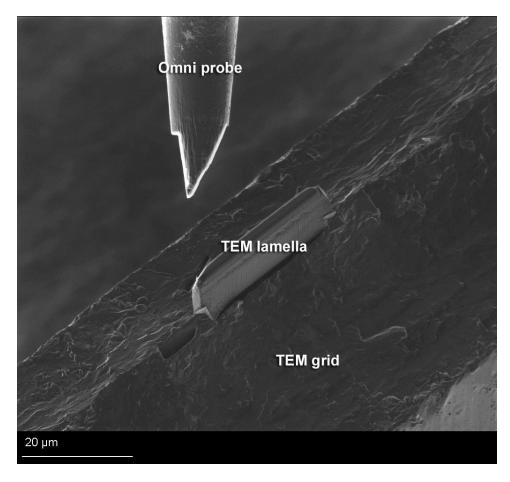

| Figure 10-14 TEM sample is fitted into a groove on TEM grid and probe is cut from the      |

| sample                                                                                     |

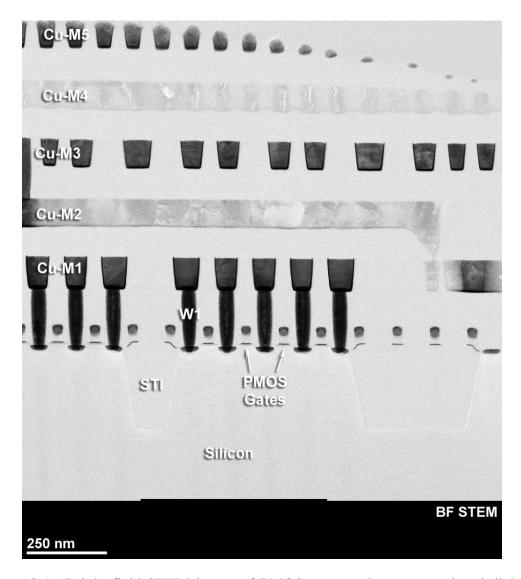

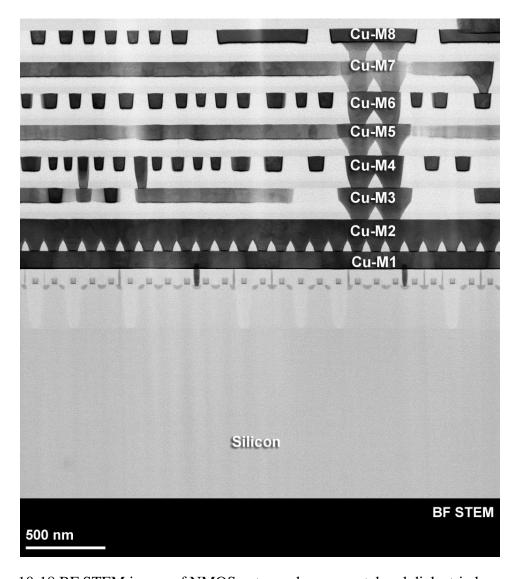

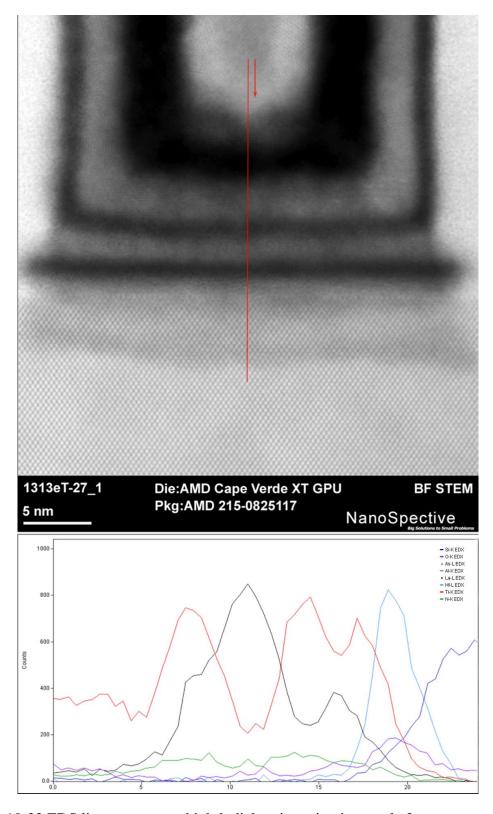

| Figure 10-15 Bright field STEM image of PMOS gates and upper metal and dielectric          |

| layers 162                                                                                 |

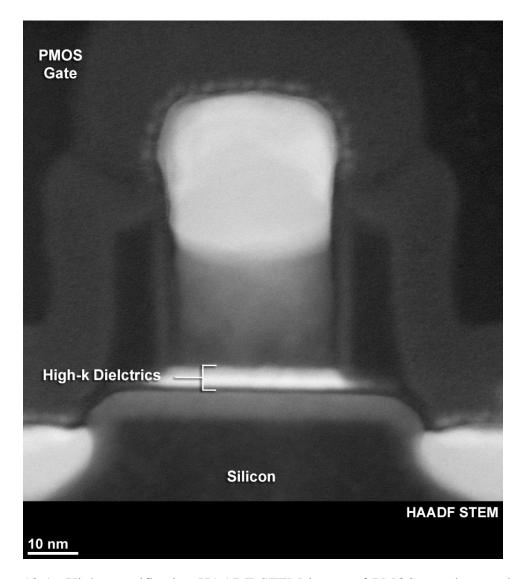

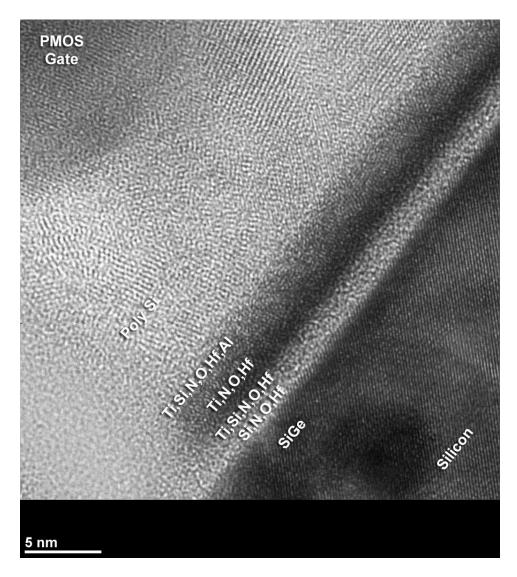

| Figure 10-16 High magnification HAADF STEM image of PMOS gate in sample one.           |

|----------------------------------------------------------------------------------------|

| Image shows the location of high-k dielectrics layer                                   |

| Figure 10-17 Ultra-high magnification of high-k dielectric region in a PMOS gate of    |

| sample 1. Compositions are obtained by EDS line scans                                  |

| Figure 10-18 BF STEM image of NMOS gates and upper metal and dielectric layers. 165    |

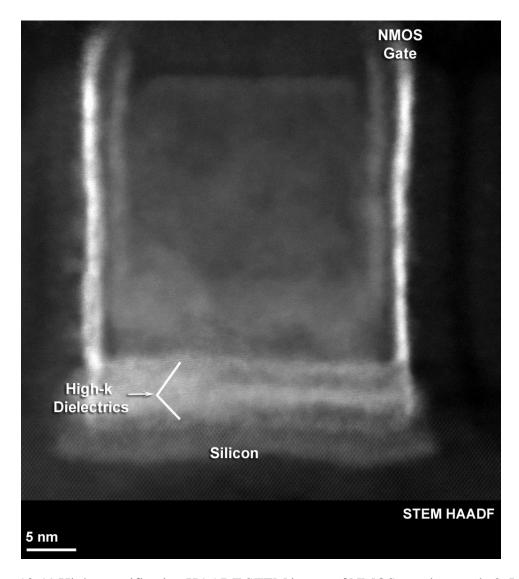

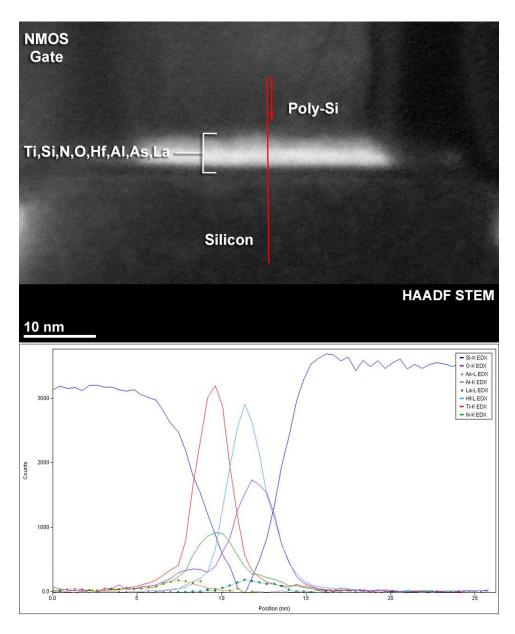

| Figure 10-19 High magnification HAADF STEM image of NMOS gate in sample 2. Image       |

| shows the location of high-k dielectrics layer                                         |

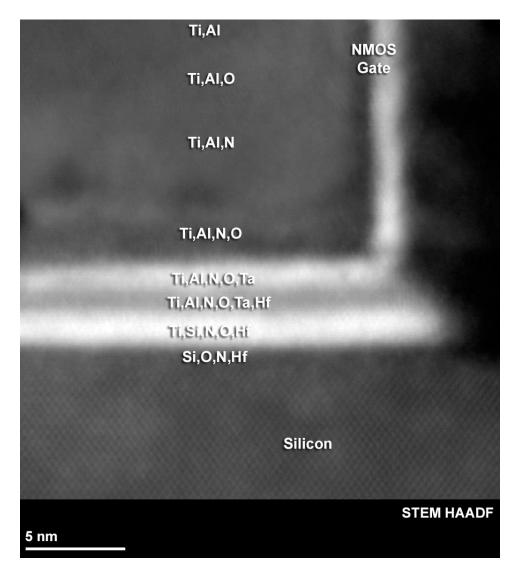

| Figure 10-20 Ultra-high magnification of high-k dielectric region in a NMOS gate of    |

| sample 2. Compositions are obtained by EDS line scans                                  |

| Figure 10-21 EDS line scan across high-k dielectric region on the NMOS gate in sample  |

| 1                                                                                      |

| Figure 10-22 EDS line scan across high-k dielectric region in sample 2                 |

| Figure 10-23 EDS line scan simulation for first sample. Beam and scan parameters were  |

| chosen same as experiments                                                             |

| Figure 10-24 EDS line scan simulation for second sample. Beam and scan parameters were |

| chosen same as experiments                                                             |

# LIST OF TABLES

| Table 8-1 Comparison of different types of electron sources. [65]                          |

|--------------------------------------------------------------------------------------------|

| Table 8-2 Parameters and final results for calculation of EDS spatial resolution in Titan  |

| TEM with 1 Å incident beam diameter and 200 KeV beam energy for 20 nm thick sample.        |

|                                                                                            |

| Table 8-3 Parameters and final results for calculation of EDS spatial resolution in Tecnai |

| TEM with 4 Å incident beam diameter and 300 KeV beam energy for 20 nm thick sample.        |

|                                                                                            |

## CHAPTER 1 INTRODUCTION

#### 1.1 History of Semiconductors

Semiconductors are materials with electric conductivity between conductors and dielectrics. The first documented semiconductor was reported by Michael Faraday in 1833 when he observed reduction of silver sulfide resistance with temperature which was different than metals. [1] Another important property of semiconductors is that their conductivity can vary over several orders of magnitude by small changes in doping concentration. [2] The next big step for semiconductors happened in 1870s. In 1874, rectification was reported in the contacts between metals and some oxides and sulfides. Carl Ferdinand Braun made the first semiconductor rectifier, which became the foundation for the most basic and simple electronic device, the diode. [2, 3] Around the same time another important application was discovered for these materials with the invention of photovoltaic cells. Research until then showed promise of electricity production by shining light to selenium and in 1883 Charles Fritts made the first photovoltaic cell. [4]

Increasing use of radio and semiconductor rectifiers showed a bright future for these materials in 20<sup>th</sup> century. Silicon is currently the most known and used semiconductor material. Silicon made its entrance into the industry in 1906 when Greenleaf Whittier Pickard demonstrated and patented [5] that silicon crystals could be used as an electromagnetic wave detector. For about 50 years diodes were used in industry while efforts were made to better understand semiconductors. All these efforts paid off when the first point contact transistors were created in 1948. Bardeen and Brattain received the Nobel Prize for this discovery, together with Shockley, in 1956. [2]

Perhaps the final step for semiconductors to conquer electronics world was done in 1954 when Gordon Teal announced the first silicon transistor at a meeting of the Institute of Radio Engineers in Ohio. [2] This was the beginning of an era for semiconductor industry.

Today it is almost impossible to find people who are not using electronic devices in one way or another in their lives, and even harder to find an electronic device that does not have a semiconductor material inside. All industries are using these devices extensively, from cars and home appliances to optoelectronic devices that transfer huge amount of data every second all around the world. Semiconductors are playing a major role in our life. Since the beginning of this industry, the number of transistors in an integrated circuit (IC) has been increasing exponentially. [1] Gordon Moore predicted this trend in 1975, later known as Moore's Law [6]. Transistors had to be miniaturized in order to fit a larger number of them in same area. This trend in industry resulted in a downscaling of devices to move from a feature size of about 10 µm in the 1970 to a 10 nm feature size in 2015.

Among various types of semiconductor devices, microprocessors play an important role. Today virtually any electronic device that has to process information uses microprocessors. The first microprocessor was the 4 bit 4004 made by Intel in 1971. [7] Many current devices use system on chip (SoC) integration where all the components of a computer are contained on a single silicon chip. Regardless of their complexity or the application of an IC, the most fundamental component is the transistor. In 2009 there were about 1 billion transistors per person on earth. [8]

# 1.2 <u>Microelectromechanical Systems and Infrared Sensing</u>

Microelectromechanical systems (MEMS) are devices of smaller than 1 mm and larger than 1 µm that use electrical and mechanical components to perform a task in an electronic device. [9] MEMS are finding more applications in various industries every year and their market is about 15 billion dollars in 2015. These devices are often employed in electronics like sensors, actuators and energy harvesters over a wide variety of industrial systems. From complex systems like space and air vehicles to health care devices like wearable systems for remote monitoring of human health, they all use MEMS and NEMS (nanoelectromechanical systems) for various purposes. Most of these devices are based on energy conversion provided by suitable coupling effect. Among all different techniques, electromechanical conversion is predominant. It provides a transformation of mechanical energy introduced by forces, moments, stresses and strains in structural components into electromagnetic energy or vice versa. [10] One of MEMS applications is in infrared sensing which we are focusing on in this research.

Bolometers are devices that absorb electromagnetic radiation and as a result of that experience temperature change which is sensed by a temperature sensing principle like change in resistivity. Uncooled infrared bolometers have become dominant for the majority of commercial infrared imaging applications. Some of the most common infrared imaging applications are thermography, night vision, mine detection, surveillance, medical imaging and industrial process control. [11]

Many of MEMS infrared detectors work based on deflection of a movable part due to change in temperature and detection of such deflection by means of a sensing principle. This can be a change in capacitance, resistance or other methods. Some of the most important parameters in the design of MEMS infrared sensors are low conductance between the bolometer and its surrounding, high absorption of the infrared radiation, low noise and a sufficiently low bolometer thermal time constant. At the same time it is important for commercial infrared imaging applications, that the bolometer pixels are as small as possible with reported pixel pitches being  $17 \, \mu m \, x \, 17 \, \mu m \, [12-14]$ . This allows for high-resolution focal plane arrays at acceptable cost. [11]

# 1.3 <u>Understanding of Semiconductor and MEMS Devices</u>

With such importance of semiconductors and MEMS devices in our daily life, there is no doubt about the ongoing need for understanding their characteristics and functions. This can be done in two ways:

- Modeling and Simulation: Regardless of size, design, function and application, all of these devices follow the rules of physics. These rules are all expressed in forms of differential equations which can be solved analytically or numerically by different modeling techniques such as finite element modeling. This step is usually done before device fabrication and is used for better understanding of device design and behavior and its optimization. This will lower the chance of unpredicted device failure after fabrication.

- Characterization: As device complexity increases, the chances of missing some aspect of it in modeling increases. It is then necessary for each

fabricated device to be analyzed by suitable techniques to ensure its proper functionality and quality. In addition to quality control, other applications for device characterization are failure analysis, research and intellectual property protection, etc.

We can look into each device in two different ways. It can be analyzed as a whole, where many parts interact with each other to perform a single function. In this case it is more important to understand the device functionality and interaction of the parts. A simple example is current–voltage characterization of a transistor where drain current is measured Vs. drain to source voltage for different values of gate voltage. We can also characterize these devices according to the characteristics of their individual parts. Type of materials, dopant concentration, resistivity, etc. are all examples of such characteristics. The first category usually requires the device to stay functional while second category of characterization requires devices to be taken apart so that individual parts can undergo different necessary characterization processes.

## 1.4 Outline of This Dissertation

In this dissertation two research projects are presented. The first project is the design, modeling, fabrication and characterization of a novel MEMS infrared detector. This project was research done to test and optimize a proposed infrared detector detailed in US Patent 007977635B2 [15] for commercialization possibilities. This project will be presented in chapters 2 through 6. The second research project is selected out of a body of work that was done by the author in collaboration with NanoSpective, Inc.[16]

NanoSpective specializes in materials science with special emphasis on nanoscale materials characterization, particularly semiconductor devices. The company provides analytical services and consultation to a worldwide market in various industries specially semiconductors, offering complete solutions for intellectual property issues, failure analysis, quality control, and materials research. The selected project is analytical and numerical modeling of energy-dispersive x-ray spectroscopy (EDS) and transmission electron microscopy (TEM) for analyzing high-k dielectric layers of 22 nm node gates structures in a microprocessor. The modeling results are compared to experimental data for the observation of material diffusion in those layers. This project is presented in chapters 7 to 10. Chapter 11 provides an overall conclusion about both projects.

Outline of this thesis for next chapters is as follows:

- Chapter 2: This chapter will provide background information from US

patent 007977635B2 [15] on proposed MEMS IR detector. After reviewing

this patent and different aspects of such device, a short description of device

design will be presented.

- Chapter 3: The main focus of the first presented project in this dissertation is on modeling and characterization of electrostatic behavior of the aforementioned MEMS IR detector. In this chapter, a semi-analytical approach is used to understand this electrostatic behavior.

- Chapter 4: Following the semi-analytical approach, this chapter presents the finite element modeling of the device. This provides a better understanding

- of its electrostatic behavior. Modeling results also provide optimized design parameters for better functionality and limits of device operation.

- Chapter 5: Using the optimized design results of the finite element analysis,

the device is fabricated. In this chapter all steps of fabrication are explained

and the final devices are presented.

- Chapter 6: Post-fabrication characterization results are presented in this

chapter. Here, different techniques for characterization of electrostatic

behavior of this device are described and experimental results are presented.

The expected behavior is compared with the results from the finite element

modeling.

- Chapter 7: In this chapter additional available techniques for characterization of semiconductor devices are reviewed. This chapter provides an introduction to the second presented research project in this dissertation.

- Chapter 8: Analytical and theoretical background for EDS and TEM resolution limits are presented in the context of the characteristics of the device under investigation.

- Chapter 9: The fundamentals of Monte Carlo simulations are explained in this chapter. The results of using this simulation technique for TEM and EDS are used to optimize the data acquisition parameters to achieve highest possible lateral spatial resolution required for analyzing the interfaces of a complex stack of thin films.

- Chapter 10: In this chapter, the presence of diffusion in the high-k dielectric layers of two advanced generation semiconductor devices are investigated by experiments. The simulation results are compared with the empirical data to validate the experimental observations.

- Chapter 11: Conclusion is made in this chapter on both research projects and industrial applications are mentioned for them.

# CHAPTER 2 PATENT REVIEW AND DEVICE DESIGN

#### 2.1 Introduction

In this chapter different aspects of a MEMS IR detector design will be presented. Fabricated device in this project was based on a patent by Oliver Edwards [15]. We will first review his design and patent's claims. Then we will analyze some of the important aspects of this design and provide optimized factors to enhance the device functionality. Based on these analyses, the final design will be introduced in detail. It is worth mentioning that we are only reporting patent claims in first part of this chapter. These claims are tested though this research and modifications are done to provide optimum device behavior. Also, most of this research is focused on investigating the claimed electrostatic behavior of this device and optimizing its design to achieve the claimed behavior. Although the finalized design is suitable for infrared detection, it also has a wide range of other applications in MEMS industry that are not necessarily associated with infrared technology.

## 2.2 Review of Preliminary Work

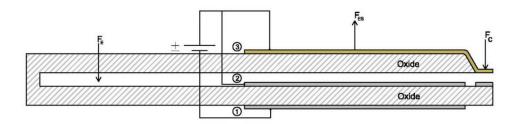

Edwards [15] proposed a MEMS infrared (IR) detector comprised of a cantilever, a surface plate, and a buried plate. Lifting of the cantilever tip from a surface contact pad by electrostatic force is an essential principle of operation, in which the duty cycle of a repetitively opened and closed tip contact is a measure of the absorbed infrared energy. [17] Figure 2-1 demonstrate overall side view of suggested design.

Figure 2-1 Simplified schematic of the device. [18]

The top and middle conductive plates are at the same bias while the bottom plate, buried under an insulating layer, is held at an opposite potential. The bottom and middle plates are fixed but the top plate is held above the surface by arms at one side and is free to move up and down on the other side which forms a cantilever. The device work principle is based on deflection due to three separate mechanisms. First, the claimed electrostatic repulsion that pushes top plate upward, second, the bending due to the difference in thermal expansion coefficient of the two different material layers in the cantilever and third, a restoring elastic force that tends to return the cantilever to its initial position after deflection.

In the absence of thermal deflection, by applying a saw tooth bias between the plates, regardless of its sign, cantilever will move up due to the total electrostatic repulsive force on it. But as the bias drops back to zero, the elastic force will restore cantilever to its initial position. The patent suggests a tip which will touch the surface once the cantilever is back to its original position. Such a tip enables an external circuit to count every time cantilever comes back to its initial position. In the absence of heat absorption, the touching frequency is the same as saw tooth bias frequency.

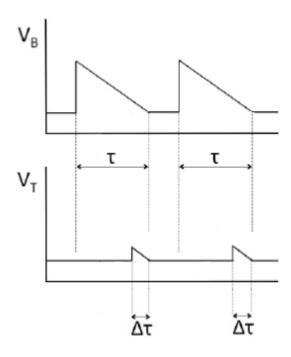

Figure 2-2 presents a schematic of the applied and measured voltage waveforms. In equilibrium the free end of the cantilever is in physical and electrical contact with the tip pad. When the cantilever is biased with a voltage  $V_B$ , an upward repulsive electrostatic force lifts the cantilever from the surface and breaks the tip contact. As  $V_B$  is ramped down during a time  $\tau$ , the voltage at the tip contact  $V_T$  is monitored. If IR radiation is absorbed, thermal deformation of the bimorph arms causes the tip to return to the tip contact sooner than  $\tau$  by a time  $\Delta \tau$ , as determined by the voltage  $V_T$  that appears on contact. The time  $\Delta \tau$  gives a temporal measurement of the absorbed IR flux. [19]

Every time tip touches the surface, heat is drained through metallic tip and makes pixel ready for next sequence. One of the advantages of this design is the absence of a cooling system and the high frame rate which makes it more suitable for infrared scene detection.

Figure 2-2 Timing diagram showing applied bias  $V_B$  and measured tip voltage  $V_T$  waveforms. [19]

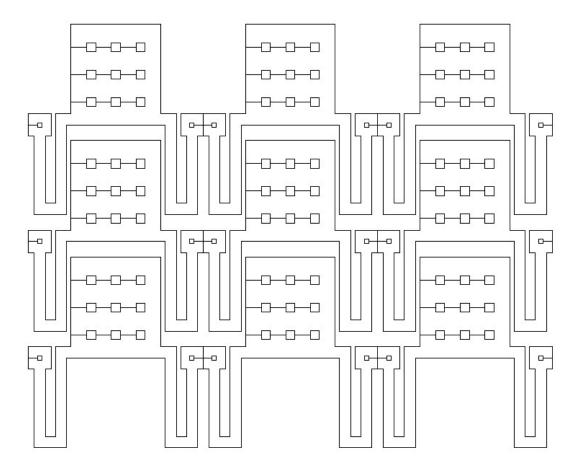

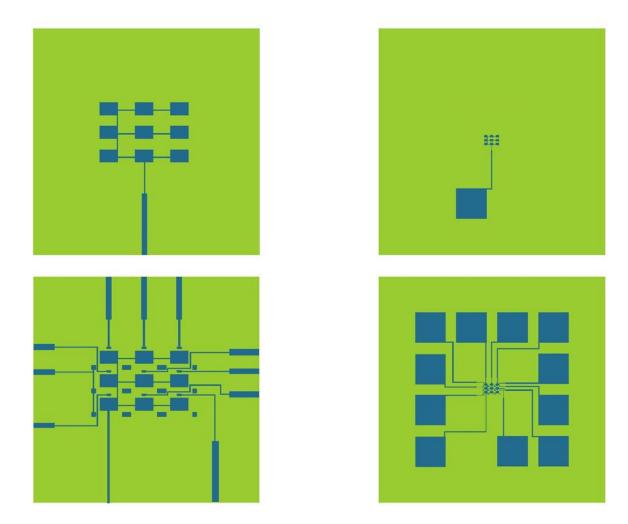

Based on single pixel design, Edward proposes an array detector like the one in figure 2-3, where the pixels are closely packed together on a surface to form an infrared scene imager. This space-efficient three-layer design makes higher fill factor possible and suggests broader applications as a means of overcoming stiction in MEMS switches, actuators, and micromirrors. [20, 21]

Figure 2-3 Focal plane array configuration of final devices.

## 2.3 <u>Design Criteria</u>

In this section we present a theoretical analysis of several design criteria for the proposed MEMS cantilever in Edward's design. The factors considered are:

- 1. The thermal bending of a bimorph arm that is anchored to the substrate.

- 2. The time constant for establishing thermal equilibrium for heated bimorph after its tip has contacted the substrate.

- 3. The electrostatic repulsion required to lift the cantilever from the surface. In this section our approach is entirely analytical, seeking simple design formulas that give quick order of magnitude estimates, which can be tested and optimized in the hardware.

For the thermal bending problem, materials, geometries, and deposition temperatures are considered as parameters. For the thermal time constant problem, the substrate is assumed to be an infinite thermal reservoir at constant temperature while heat flow from a warm cantilever of small heat capacity through a cylindrical contact is considered. Finally, the electrostatic repulsion problem is solved using energy methods considering forces between conductors held at constant potential. The resulting formulas are useful for the final design of any MEMS-based thermal sensor and bolometer.

# 2.3.1 Thermal Bending

In a bilayer cantilever, due to the difference in thermal expansion coefficients of layers, thermally induced stress will bend the surface upward or downward. The stress is:

$$\sigma_{mismatch} = \frac{E}{1-\nu} (\alpha_f - \alpha_s) (T_d - T_r)$$

(1)

Figure 2-4 demonstrates the described bending for two different cases.

b. When coating has lower coefficent of thermal expansion than substrate.

Figure 2-4 Demonstration of double layer system bending due to differences in thermal expansion coefficient of layers.

For a thin film on thick substrate this is [22]

$$\sigma_f = \frac{E_S t_S^2}{6Rt_f (1 - v_S)} \kappa \tag{2}$$

The deflection is usually very small and hence having the two equations equal, will lead to

$$h(t) = \frac{{}_{3}E_{f}t_{f}L^{2}}{{}_{5}t_{s}^{2}}(\alpha_{f} - \alpha_{s})(T - T_{d})$$

(3)

Where L is cantilever's length, E is young module,  $\alpha$  is thermal expansion coefficient,  $t_f$  is film thickness,  $t_s$  is substrate thickness and  $T_d$  is deposition temperature. Taking the first derivative of tip's deflection with respect to temperature we find:

$$\frac{dh}{dT} = \frac{3E_f t_f L^2}{E_S t_S^2} (\alpha_f - \alpha_S) \tag{4}$$

This value can be interpreted as cantilever sensitivity to temperature change and will have a great impact on proposed device functionality. Based on this value, better choices for materials can be made. Ideally higher values of thermal sensitivity are required. For example, a choice of Al as thin film on top of silicon oxide will lead to 0.095  $\mu$ m/K while Zn over SiO<sub>2</sub> will have 0.192  $\mu$ m/K sensitivity. Chosen materials in device fabrication are presented in chapter 5.

#### 2.3.2 Thermal Time Constant.

Infrared sensors have different mechanisms to drain absorbed heat. [23] In this design heat is drained through metallic tip once it touches the surface. In such mechanism tip design will have a great impact on how long it takes the device to get in thermal equilibrium with substrate. So it is important to have an estimation of this time constant.

Here we consider the substrate an infinite thermal source fixed at a constant temperature of 300 K. The heat flux is:

$$H = KA \frac{(T_2 - T_1)}{L} = c_1 m_1 \frac{dT_1}{dt} \tag{5}$$

With proper boundary conditions, the solution is:

$$T_1(t) = T_2 + e^{t/\tau} (T_{1i} - T_2) \tag{6}$$

Where thermal time constant is defined as:

$$\tau = \frac{c_1 m_1 L}{KA} \tag{7}$$

This time constant gives us a measure for how fast heat is leaving the cantilever once the connection between tip and substrate is established. For a gold tip, with its length  $L=2~\mu m \ \text{the thermal time constant is about } 5.5\times 10^{-6}\, \text{s}.$

This corresponds to 1.8 MHz frequency. Thus, in principle, thermal zeroing through periodic tip contact can allow high frame rates without chopping.

### 2.3.3 Thermomechanical Noise

Thermomechanical noise for a MEMs-based infrared detector using null switching [15] depends on vibrational amplitude, since IR radiation is transduced to a change in the duty cycle of a repetitively closing switch. Equipartition theorem determines the maximum rms vibrational amplitude for the fabricated cantilever switch at its natural frequency. This determines the worst case timing uncertainty. [19]

In this section we discuss thermomechanical noise. This detector is unusual in that absorbed IR radiation is transduced into a measurement of a time. High sensitivity to small differences in scene temperature requires high measurement bandwidth. Thermomechanical noise is determined by this bandwidth rather than by the frame rate, as in usual imaging detectors. Thus, the vibrational amplitude at the cantilever's natural oscillation frequency is important.

A simplified schematic of the MEMS cantilever device is presented in figure 2-1. The tip of the cantilever consists of a tip contact that is normally touching a surface tip pad ("null position"), allowing electrical sensing of contact. An upward electrostatic force F<sub>ES</sub> appears when the device is biased as shown in [18, 24]. This is opposed by an elastic

restoring force  $F_E$  and a sticking force  $F_C$  (such as Casimir force).[25] The latter force will be ignored here. For simplicity we will consider the elastic force to apply mainly to the arms and we ignore any deformation of the metal-coated regions. Thermo-mechanical vibration of the cantilever results in uncertainty in the time of contact, and hence noise in the determination of IR flux. [17]

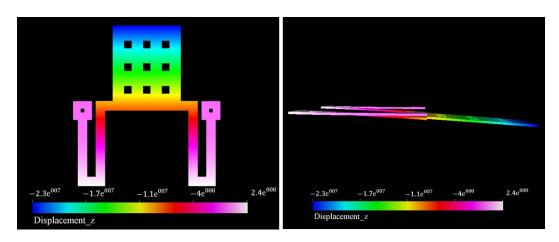

Key to the estimation of thermo-mechanical noise is an estimate of the elastic constants of the device, i.e. its spring constant when considered as a 1D simple harmonic oscillator. Figure 2-5 presents solved stress field and displacement of the cantilever. This calculation was done assuming Aluminum as the material, with Poisson ratio 0.35, Young's modulus 70 GPa, and density 2700 kg/m³. The cantilever is fixed to the substrate at its anchors. It is subjected to a stress of 154 N/m² as a result of uniformly distributed force on its 20 x 18  $\mu$ m² area plates. Color indicates vertical displacement. Blue is the maximum displacement in the negative z direction, while white is the maximum displacement in positive z direction. The anchors are fixed at z = 0, which is color-coded light purple. For these calculations, the equilibrium position of the cantilever tip is at z = 0, in contrast to that actual device, where the cantilever is bent down with the tip touching the surface 2  $\mu$ m below the anchor point for the isolation arms. But this should make only a little difference in the value of the spring constant determined.

Figure 2-5 shows that the elbows on the arms bend upward by  $\sim 10\%$  of the amount that the tip bends down. From the top view color gradient, one sees that the bimorph arms (inner pair) have more curvature than the isolation arms (outer pair). Thus, the elastic restoring force is primarily due to the inner pair of arms.

A plot of force as a function of displacement is linear. We found for an Aluminum cantilever that the spring constant K has the value 0.73 N/m. (Aluminum is considered for comparison to some macroscopic machined models that we experimented with.) For SiO<sub>2</sub>, as in the actual cantilever, K = 0.68 N/m.

Figure 2-5 (Left) Top view of deflection map due to the stress caused by uniformly applied pressure of 154 N/m2 applied to the rigid 20 x 18  $\mu$ m<sup>2</sup> cantilever plate. (Right) Side view of the cantilever displacement scaled up by a factor of 10. [19]

Suppose the cantilever is an un-damped one-dimensional oscillator with natural frequency  $\omega_0$ . The equipartition theorem indicates that the mean square amplitude of the vibrations should not be less than

$$\left(\frac{1}{2}\right)K < z^2 > = \left(\frac{1}{2}\right)k_B T \tag{8}$$

If we take the spring constant to have the value K=0.68~N/m, we find the rms vibrational amplitude to be 79 pm. This value is 4000x larger than the value given in [17] from a published thermomechanical noise formula assuming 30 Hz bandwidth. The reason for the difference is that 30 Hz is far from the ~200 kHz natural frequency of the cantilever

(mass ~13 ng). The amplitude of oscillations at 30 Hz is small because this frequency is far out on the wing of the vibrational resonance line shape.

The detector mode of operation requires high electronic bandwidth to differentiate small timing differences that indicate small differences in scene temperature. Since timing measurements may be done with reference to quartz stable clocks operating easily at 20 MHz or more, the natural frequency of the cantilever will be within the measurement bandwidth. Thus, timing uncertainty (i.e. noise) is determined by the natural frequency where vibrational oscillations are maximum.

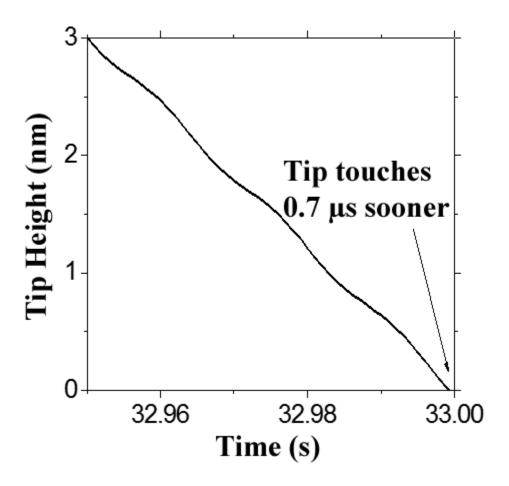

To illustrate, figure 2-6 presents the final 50  $\mu$ s of the tip-height saw-tooth with superimposed thermal noise at the natural frequency. The tip touches early by 0.7  $\mu$ s. We may demonstrate mathematically that the timing uncertainty depends primarily on noise amplitude as follows. For frame rate f and noise frequency  $\omega$ , the tip height is

$$z(t) = z_0(1 - 2ft) + A \cos\left[\omega t + \phi\right] \tag{9}$$

The time of contact is determined by setting the left side to zero and solving for t. When the noise amplitude A=0, touch down occurs at time  $\tau=1/2f$  (50% duty is assumed). The maximum timing error occurs when  $Cos=\pm 1$ , for which the maximum timing uncertainty is  $\pm A/(2 f z_0)$ . This timing uncertainty depends on A, but it does not depend on  $\omega$ . Thus, thermomechanical noise is mainly defined by noise at the natural frequency of the cantilever, where amplitude is largest, which will be a function of device shape and materials. It is outside of the scope of this dissertation to investigate noise calculation aspect any further, but the author emphasizes that noise consideration has to be done in the design of commercialized products that are based on this design.

Figure 2-6 Tip height ramp vs time with superimposed vibrational noise. [19]

The most novel and important aspect of this device is in electrostatic repulsion on cantilever which we will study in detail in next chapters.

# 2.4 <u>Device Design</u>

Although we tried to keep design aspects similar to what Edward describes [15] it is important to know that patent design is only preliminary and all aforementioned factors as well as many other parameters such as fabrication feasibility, cost, available methods and time had to be considered in final design of the device. During three phases of this

project and over about 3 years we had to change details of the design to optimize its functionality and customize it for our purposes and capabilities. What is described in the following paragraphs is the finalized design considering all of these considerations.

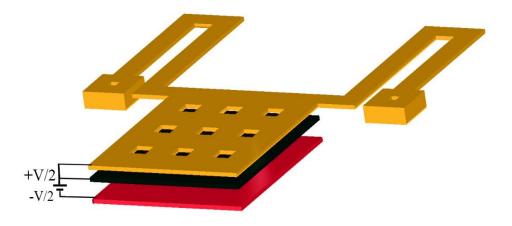

Overall 3D demonstration of a single pixel can be seen in figure 2-7. As mentioned previously, each pixel consists of three plates. A bottom plate shown in red is buried under the substrate surface. A middle plate is fixed on the substrate surface. The distance between these two plates is 500 nm. The third plate is part of the actual cantilever which is held above the surface. The main parts of cantilever are as follow:

- 1. Anchors: anchors are the only parts of cantilever who are permanently in contact with surface. Each pixel has two anchors, one on each side. Anchors are made 10  $\mu$ m  $\times$  10  $\mu$ m. Each anchor has a hole that connects its top metallic surface to substrate. This hole ensures electrical connection between top plate and external circuitry that provides bias between plates.

- 2. Isolation arms: these are the arms that are connected to the anchor. These arms are made of 500 nm dielectric material with a thin layer of metal on top. This metal layer is continues all over the surface of cantilever and is in charge of making the connection between top plate and external bias source.

- 3. Bimorph arms: bimorph arms are double layers of dielectric material and thick layer of metal. These ensure thermal bending once cantilever changes temperature. Choice of length, thickness and material on these arms define thermal time constant as explained before.

- 4. Absorber layer: An absorber material is deposited on top of top plate which enhance thermal absorption and sensitivity of the device.

- 5. Release holes: Fabrication process requires release of cantilever from the sacrificial layer that device is built on. Such release is only possible by making holes on top plate that ensure uniform access to sacrificial layer for etching.

- 6. Tip: tip is only added for final devices when its functionality is tested by touching the sensing pad on the surface. It is hidden under top plate and is touching sensing pad in natural position. However by applying the bias it will disconnect from the surface.

Parts mentioned above are only main parts of this device. In chapter 6 we will explain details of fabrication including all materials, dimensions and techniques used to fabricate the actual device.

Figure 2-7 Overall structure of the device.

# CHAPTER 3 SEMI-ANALYTICAL APPROACH

### 3.1 Introduction

As we mentioned earlier the focus of this dissertation is on understanding the electrostatic behavior of this device. We are specifically more interested in demonstrating presence of repulsive electrostatic field in a three plate configuration of this device. We will then further analyze different parameters of design to find an optimum configuration in which this force will be maximized. In this chapter, our approaches for analytical calculations of total electrostatic force applied on the top plate will be explained and a simple example of 2 plate system will be solved. Then we will explain three plate problem present in this device and solve that using similar technique. Using calculated solution for total electrostatic force we will show how plate movement will affect this force.

### 3.2 Electrostatic Field in a System of Conductors

We start our method by calculation of electrostatic force produced by conductors. It is a fundamental proven fact the electric field inside a conductor is always zero. That is because any electric field in a conductor will cause a current which then results in dissipation of energy. Hence it is impossible to have an electric field inside a conductor in the absence of external source of energy. This follows that all charges in a conductor have to be on the surface and cannot be inside conductive medium. This means that in system of conductors, electrostatic problems are reduced to calculating fields outside the conductors' volume. [26] Such system has to satisfy Laplace's equation in the vacuum:

$$\Delta \phi = 0 \quad \& \quad \mathbf{E} = -\nabla \phi \tag{10}$$

Where  $\mathbf{E}$  is electric field vector and  $\boldsymbol{\Phi}$  is electric potential. Using these equations and having no electric field inside a conductor results in a conclusion that electric field on the surface of a conductor is perpendicular to the surface. [26] On the other hand, perpendicular component of electric field (in Gaussian units) is related to charge distribution on the surface by:

$$\mathbf{E}_{n} = \frac{\partial \phi}{\partial n} = 4\pi\sigma \tag{11}$$

Where  $\sigma$  is the surface charge density.

Hence the total charge on the conductor is equal to:

$$q = \frac{-1}{4\pi} \oint \frac{\partial \phi}{\partial n} \, df \tag{12}$$

# 3.3 Energy in Electrostatic Field of Conductors

Energy in electrostatic field of system of conductors can be written as:

$$U = \frac{1}{8\pi} \int E^2 dV \tag{13}$$

Integral is taken over all spaces outside all conductors. We can take this further:

$$U = -\frac{1}{8\pi} \int \mathbf{E} \cdot \nabla \phi \, dV = -\frac{1}{8\pi} \int \nabla \cdot (\phi \mathbf{E}) \, dV + \frac{1}{8\pi} \int \phi \, \nabla \cdot (\mathbf{E}) \, dV$$

(14)

Second integral is zero since div  $\mathbf{E} = 0$ . We can bound first integral to volume between surface of conductors and infinitely far away surface. Second boundary results in zero since electric field will be zero at infinite distances from the field source (in this case charges on conductor surface). Since potential is constant on surface of each conductor we can rewrite energy of the system in following form:

$$U = \frac{1}{8\pi} \sum_{i} \boldsymbol{\phi}_{i} \oint E_{n} \, df \tag{15}$$

Where  $\Phi_i$  is the constant potential on the  $i^{th}$  conductor's surface. Using equation 12 we can express energy as:

$$U = \frac{1}{2} \sum_{i} q_{i} \boldsymbol{\phi}_{i} \tag{16}$$

Where  $q_i$  is the total charge on  $i^{th}$  conductor. Since field equations are linear and homogeneous charges and potentials of conductors must have a linear relation which can be expressed in a general form of:

$$q_i = \sum_i C_{ij} \boldsymbol{\phi}_i \tag{17}$$

Where  $C_{ij}$  are called coefficients of electrostatic induction and  $C_{ii}$  are called coefficients of capacity. These numbers depend on shape and relative positions of conductors and are related to linear dimensions of conductors. We can express equation 17 in a matrix form of:

$$\begin{bmatrix} q_1 \\ \vdots \\ q_n \end{bmatrix} = \begin{bmatrix} C_{11} & \cdots & C_{1n} \\ \vdots & \ddots & \vdots \\ C_{n1} & \cdots & C_{nn} \end{bmatrix} \begin{bmatrix} \boldsymbol{\phi}_1 \\ \vdots \\ \boldsymbol{\phi}_n \end{bmatrix}$$

(18)

It can be seen from symmetry or proven analytically [26] that

$$C_{ij} = C_{ji} \tag{19}$$

Using equation 12 we can rewrite equation 16 as:

$$U = \frac{1}{2} \sum_{i,j} C_{ij} \phi_i \phi_j = \frac{1}{2} \sum_{i,j} C_{ij}^{-1} q_i q_j$$

(20)

Since energy is always positive, it is easy to see that

$$C_{ii} > 0 \tag{21}$$

$$C_{ij} < 0 \quad (i \neq j) \tag{22}$$

# 3.4 System of Two Flat Conductors

Let us examine our calculation with a simple example first. Imaging a conventional capacitor. Where two infinitely large flat conductors are separated with distance d from each other. One plate has –q and the other has +q charge on themselves. So we can write equation 18 for this system as:

$$\begin{bmatrix} -q \\ +q \end{bmatrix} = \begin{bmatrix} C_{11} & C_{12} \\ C_{12} & C_{22} \end{bmatrix} \begin{bmatrix} \phi_1 \\ \phi_2 \end{bmatrix}$$

(23)

Similarly we can express energy of the system using equation 20 in following form:

$$U = \frac{1}{2} \sum_{i,j} C_{ij}^{-1} q_i q_j = \frac{1}{2} (C_{11}^{-1}(-q)(-q) + C_{12}^{-1}(-q)(+q) + C_{21}^{-1}(+q)(-q) + C_{22}^{-1}(+q)(+q) = \frac{1}{2} (C_{11}^{-1}q^2 - 2C_{12}^{-1}q^2 + C_{22}^{-1}q^2)$$

(24)

Where inverse matrix of C is:

$$C_{ij}^{-1} = \frac{1}{c_{11}c_{22} - c_{12}^2} \begin{bmatrix} c_{22} & -c_{12} \\ -c_{12} & c_{11} \end{bmatrix}$$

(25)

Hence:

$$U = \frac{1}{2} \frac{(C_{22} + 2C_{12} + C_{11})}{C_{11}C_{22} - C_{12}^2} q^2 \tag{26}$$

Comparing this results with conventional definition of energy for a parallel plate capacitor:

$$U = \frac{1}{2}q^2/C \tag{27}$$

We can have the relation between conventional capacitance for a parallel plate capacitor and capacitance coefficient as follows:

$$C = \frac{\varepsilon_r A}{4\pi d} = \frac{C_{11}C_{22} - C_{12}^2}{C_{22} + 2C_{12} + C_{11}} \tag{28}$$

Assuming a symmetry between two plates it is reasonable to consider diagonal elements equal to each other and in the order of linear length of the plate.

$$C_{11} = C_{22} \sim L \tag{29}$$

We will use this later to provide a handwaving argument for repulsive electrostatic force in three plate system.

## 3.5 Three Parallel Plate Problem: Real Case

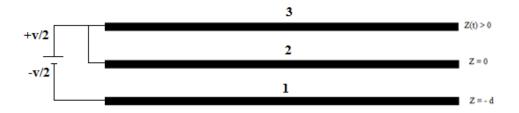

The net force on the cantilever is determined from the position dependence of the coefficients of capacitance and electrostatic induction. All of these coefficients depend on the conductor shapes, sizes, and relative positions. The model system consists of 3 parallel plates (figure 3-1), which are assumed square and each with area A. A buried plate (1) is at depth d below the surface and is held at a potential of -V/2. A fixed surface plate (2) is held at potential +V/2. The cantilever (3) is a variable height z above the surface plate, to which it is electrically connected so that its potential is also +V/2. The energy of a system of conductors at fixed potential is

$$U = \frac{V^2}{8} \left( -2C_{12} - 2C_{13} + 2C_{23} + C_{11} + C_{22} + C_{33} \right) \tag{30}$$

Differentiation of this energy with respect to the vertical position z of the cantilever gives the electrostatic force on it:

$$F = +\frac{\partial U}{\partial z} = \frac{V^2}{8} \left[ -2\frac{\partial C_{12}}{\partial z} - 2\frac{\partial C_{13}}{\partial z} + 2\frac{\partial C_{23}}{\partial z} + \frac{\partial C_{11}}{\partial z} + \frac{\partial C_{22}}{\partial z} + \frac{\partial C_{33}}{\partial z} \right]$$

(31)

It is very important that the "+" appears before the derivative in Eq. 3, rather than the usual "-" from ordinary mechanics. The quantity U is the electric energy of the plates alone, and it does not include the energy of the large charge reservoirs, batteries, or power supplies that are necessary to maintain the plates at constant potential as the cantilever moves. The energy of these charge sources or sinks do work in moving charges to maintain the potentials, so their energy changes. When this is properly included, it turns out that it is the positive derivative of U that determines the force [26].

## 3.6 Repulsive Electrostatic Force

It is important to show that total electrostatic force applied on top plate is repulsive and find out what conditions are required for this to be valid. First we present a handwaving argument that proves the force to be repulsive in simplified conditions. We can simplify three plate system to three individual systems of two plates. Figure 3-1 has a simplified diagram of this problem.

Figure 3-1 Schematics of simplified three plate system for this device.

In such case, using equation 29 and 28 to solve off-diagonal elements in terms of plates' distances and dimensions results in:

$$C_{12} = \frac{-L^2}{2\pi d}$$

$C_{13} = \frac{-L^2}{2\pi(d+z)}$   $C_{23} = \frac{-L^2}{2\pi z}$  (32)

Putting these definitions back into equation 31 and taking z derivative of each term we get the force in terms of our system configuration as follows:

$$F = \frac{V^2 L^2}{8\pi} \left( \frac{-1}{(d+z)^2} + \frac{1}{z^2} \right) > 0 \tag{33}$$

This force is always positive meaning it is upward and repulsive on top plate. It is important to notice that this is a handwaving argument and is not intended to give accurate values for total electrostatic force on the plate.

To drive a more accurate value for total electrostatic force on top plate we used a commercial software called FastCap [27] to calculate each coefficient and use equation 31 to drive total force. Figure 3-2 (upper) plots the six z-dependent coefficients calculated by FastCap for 10  $\mu$ m x 10  $\mu$ m plates. As z increases, the magnitude of  $C_{13}$  decreases due to fringe-field weakening, which lessens induced charges. Generally, however, the z-dependence of all the  $C_{1j}$  is very weak, because the surface plate screens the buried plate from the field of the cantilever, whose motion therefore has little effect on the buried plate's total charge. [18] This allows us to ignore the derivatives of those three coefficients in equation 31, giving:

$$F \cong \frac{V^2}{8} \left[ 2 \frac{\partial C_{23}}{\partial z} + \frac{\partial C_{22}}{\partial z} + \frac{\partial C_{33}}{\partial z} \right] \tag{34}$$

Figure 3-2 (upper) Coefficients  $C_{ij}$  for system of three parallel square plates as a function of the cantilever height z for plate area 10  $\mu m$  x 10  $\mu m$ . Inset: log-log plot for three of the curves. (lower) Net force on 10  $\mu m$  x 10  $\mu m$  cantilever vs. its height above the surface for 20 V bias. Symbols are calculation results. The line is a fit to  $\frac{1}{\sqrt{z}}$ . Inset: Model schematic. [18]

The induction coefficient  $C_{23}$  (which is negative) approaches zero with increasing separation of the two upper conductors, as expected, so that  $dC_{23}/dz$  is positive. The

positive coefficients of capacity  $C_{22}$  and  $C_{33}$  are expected to decrease to constant positive values as the separation between the top two conductors increases, and we expect  $C_{22} > C_{33}$  because the surface plate is near to two plates while the cantilever is near to just one. These expectations are also confirmed in figure 3-2, upper. Thus the z derivatives of these coefficients of capacity are negative. The inset in figure 3-2 upper presents a log-log plot of the three coefficients in equation 34. The slope of  $-C_{23}$  is more negative than the slopes of the other two, so that the first term in equation 34 exceeds the sum of the magnitudes of the other two terms. Hence, the total force is positive. In other words, the direction of the force is the same as if the cantilever is being *repelled from* the surface. (We eschew the convenience of phrases such as "repulsive force" and "repelled by the surface" to avoid conceptual controversies associated with the fiction of force at a distance. Each conductor feels only the negative pressure due to the fields at its own surface [26]. Integration of this pressure over the surface gives the net force [24] and confirms the sign found here.)

Figure 3-2 (lower) plots the calculated force (equation 34) using coefficient values from figure 3-2 (upper). The net force is positive in the considered range  $0.25 \, \mu m < z < 2.5 \, \mu m$ , which are the motional limits in the experimental device. The force decreases as the separation increases. Over the range considered, the force is adequately described by a power law. The line shows a fit to the function  $\frac{1}{\sqrt{z}}$ . That line reveals a small oscillation with z in the force data, which is an artifact due to meshing, as determined using higher mesh density at the expense of longer calculation times. When the permittivity of the structural oxide in the actual device is included [24], the force magnitude increases nearly four-fold in comparison to that presented in figure 3-2 for the simple model system.

## 3.7 Conclusion

In this chapter we used energy formalism to derive total electrostatic force on top plate in a MEMS device. Using this formalism we calculated total force as function of capacitance matrix elements. Using two separate approaches of handwaving argument based on dimensional analysis and direct calculation of capacitance coefficients we showed this force will be toward positive z direction meaning an upward or repulsive (with respect to substrate) on top plate. We furthered analyzed behavior of each capacitance matrix element and explained its behavior with change in vertical position of top plate.

Without a surface plate, the force on the cantilever would be downward toward the oppositely biased buried plate. On the other hand, if the surface plate were much larger than the others, it would screen the buried plate so that there would be no fields from it at the cantilever, and hence no force on the cantilever. As found above, the force is upwards for plates of equal dimensions. Thus, were the surface plate to increase in size monotonically from zero, the force would change from downward to upwards before decreasing again to zero. There will be an optimum surface plate size that maximizes the upward force.

Further understanding of device electrostatic behavior requires more complicated model that consider other factors such as plates with different sizes and different dielectric constant in between. We will approach this problem in next chapter by finite element analysis to achieve more in-depth understanding of this device.

## CHAPTER 4 FINITE ELEMENT MODELING

### 4.1 Introduction

In previous chapter we used theoretical analysis based on values of position-dependent coefficients of capacitance and electrostatic induction to demonstrate the sign of the force on the cantilever and determines its magnitude. In this chapter we use finite element simulations of local fields to confirm these results and give the distribution of the force across the cantilever. Size and motion effects have been studied. Finally an optimum design is suggested to achieve highest repulsive force and best performance.

First we will explain fundamentals of finite element analysis and software we used. Then we will explain our model and its elements. We will then go through our simulation results and their interpretation. Finally we conclude with optimum factors to achieve highest possible electrostatic response from our device.

#### 4.2 Fundamentals of Finite Element Modeling